版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、中国科学技术大学电子工程与信息科学系2内容6B-总线的概念6B-6B-总线原理微机系统的内总线标准一、从PC/XTIChanne到EISA二、局部总线:从VISA到PCI-Express6B-几种常用的外总线标准一、通用串行总线USB三、IDE和EIDE简介二、IEEE1394总线简介四、SCSI总线简介中国科学技术大学电子工程与信息科学系36B-总线的概念一、总线和总线的产生总线是计算机系统中传输数字信息的通信信道, 相当于人体中的“中枢神经”。从物理上看,总线由一些电导体的互连组成,其 具体实现形式随相互通信的设备的种类和距离而 异,可以是印刷线、印刷电路板边缘连接器、多 路电缆等。总线通

2、信的规则,或称“协议”,是决定微计算机 系统结构的基本因素之一。中国科学技术大学电子工程与信息科学系系统早期的互联方式分散连接/内部连线十分复杂,布线困难/扩展性差J效率高4控制器输出设备运算器输入设备存储器中国科学技术大学电子工程与信息科学系现代的系统互联方式总线连接5J 优点:简洁,协调扩展性好/ 缺点:有共享竞争问题1970年DEC公司PDP-11小型计算机首次采用总线技术UniBUS(单总线)。1976年用了由TS公司在世界上第一台微型计算机Altair采余爱好者定义的总线S100。I/deviceI/device主机I/Interface(adapter)I/Interface(ad

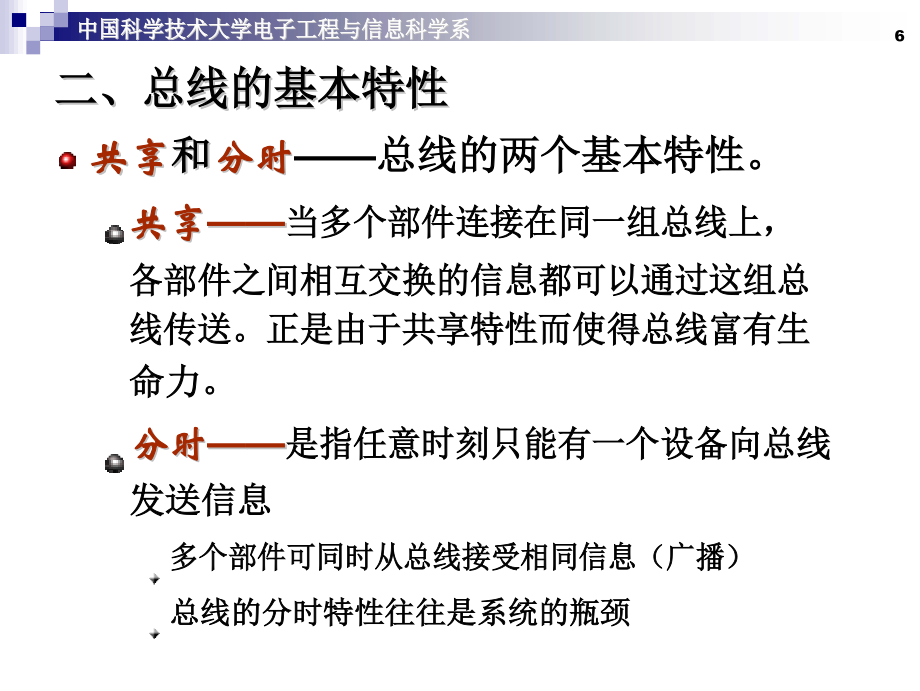

3、apter)memoryprocessor中国科学技术大学电子工程与信息科学系6二、总线的基本特性共享和分时总线的两个基本特性。 共享当多个部件连接在同一组总线上,各部件之间相互交换的信息都可以通过这组总线传送。正是由于共享特性而使得总线富有生 命力。分时是指任意时刻只能有一个设备向总线发送信息多个部件可同时从总线接受相同信息(广播) 总线的分时特性往往是系统的瓶颈中国科学技术大学电子工程与信息科学系7三、总线的分类按照物理接口分类电按照式主板式、背板式气特性分类单端方式与差分方式按照控制特性分类同步总线、异步总线和半同步总线按照通信方式分类串行总线和并行总线中国科学技术大学电子工程与信息科学

4、系更多的是按照总线位置分类8片内总线(I部,连接CPUChiBus,位于CPU的内件;部的各芯片总线(Coponent-LeveBus)。连接CPU和外围内总线(B片,例如Motel总线;rd-LeveBus),又称为板级总线或系统总,用于系统内部各高速模块之间的互连。例如ISA、EISA、PCI等;外总线(CommunicatioBus),又称I/O总线或通信总线,用于计算机之间,或者计算机与外设之间的互连。例如SCSI、USB等。本章介绍内容中国科学技术大学电子工程与信息科学系9中国科学技术大学电子工程与信息科学系10每一类(并行)总线中又分为:数据总线(DB)双向三态,传输数据信号线的条

5、数也称为总线宽度;地址总线(AB)三态,仅主设备可驱动,宽度与寻址空间有关;控制总线(CB)传送控制 命令和状 态,有些 三态,有 些非三态。中国科学技术大学电子工程与信息科学系11四、总线特性为了保证总线与部件之间机械上的可靠连接, 必须规定其机械特性;为了保证电气上正确 连接,必须规定其电气特性;为了正确传输信息,必须规定其功能特性和时间特性。背板式总线示意图中国科学技术大学电子工程与信息科学系12五、总线性能指标总线宽度:是指数据总线的根数,用bit(位) 表示,如8位、16位、32位、64位(也即8根、16根、32根、64根数据线)。最大传输率 (总线带宽):总线本身所能达到的最高传输

6、速率,用MB/s或MBps(每秒多少兆 字节) 表示。例:总线工作频率33.3MHz,总线宽度32bit,则最大传输率33.3×32÷8132MB/s。中国科学技术大学电子工程与信息科学系时钟同步/异步:总线上的数据与时钟同步工作的总线称为同步总线,与时钟不同步工作的总线称为异步总线。总线复用:为提高总线的利用率,将地址总线和数据总线共用一组物理线,在某一时刻该总线传输地址信号,另一时刻传输数据信号或命令信号。信号线数:即地址总线、数据总线和控制总线三种总线的根数总和。13中国科学技术大学电子工程与信息科学系总线控制方式:包括并发工作、自动配置、仲裁方式、逻辑方式、计数方式

7、等。14负载能力:通常用可连反映总线的负载能力。扩增电路板数来由于不同的电路对总线的负载是不同的,即使同一电路在不同的工作频率下,总线的负载也是不同的。因此,总线负载能力的指标是不太严格的。其它:如电源电压等级、能否扩展等。中国科学技术大学电子工程与信息科学系15内容6B 1 总线的概念6B 2 总线原理6B 3 微机系统一、从PC/XT的内总线标准O Channl 到EISA二、局部总线:从VISA到PCI-Express6B 4 几种常用的外总线标准一、通用串行总线USB三、IDE和EIDE简介二、IEEE1394总线简介四、SCSI总线简介中国科学技术大学电子工程与信息科学系166B 2

8、 总线原理一、总线的结构二、同步和异步通信方式三、总线的信息传输方式四、总线使用权分配中国科学技术大学电子工程与信息科学系17一、总线的结构单总线结构双总线结构多总线结构中国科学技术大学电子工程与信息科学系181、单总线结构单总线结构将CPU、主存、I/O设备(通过I/O接口)系统总线都挂到一组总线上,允许I/O之间、I/O与主存之间直接交换信息。CCPPUUIIOO接口IIOO接口内存这种结构简单,便于扩充。 但是,由于所有的传送都通过这组总线,容易形成计算机系统的瓶颈。设备00设备nn为解决CPU、主存与IO设备之间传输速率的不匹配问 题,实现CPU与其它设备的相对同步,又出现双总线结构。

9、中国科学技术大学电子工程与信息科学系192、双总线结构特点:将速度较低的I/O设备从单总线上分离出来,单独设置一条与主存总线独立的I/O总线。原理:通道是一个专门负责IO的处理器,接替CPU对I/O设备进行统一管理,以完成外部设备与主存之间的数据传送。主存总线的吞吐能力不受慢速设备的影响。主存总线CCPPUU内存通道I/O总线IIOO接口IIOO接口设备00设备nn思路:若将速率不同的I/O设备进行分类,再将它们连接在不同的通道上,通道的利用率将会进一步更高 Æ 多总线结构。中国科学技术大学电子工程与信息科学系203、三总线结构系统总线分为以下三个层次主存总线I/O总线DMA总线/

10、主存总线与DMA总线不能同时对主存进行访问。I/O总线CCPPUU主存总线DMA总线IIOO接口IIOO接口IIOO接口内存内存设备11设备nn高速外设中国科学技术大学电子工程与信息科学系214、四总线结构为了进一步提高I/O的性能,又出现了四总线结构。局部总线、系统总线、高速总线、扩展总线局部总线系统(主存)总线CCaacchhee/桥/桥桥CCPPUU主存高速外设接口SSCCSSII图形多媒体局域网高速总线低速外设接口FFAAXX扩展总线接口调制解调器串行接口扩展总线中国科学技术大学电子工程与信息科学系226B 2 总线原理一、总线的结构二、同步和异步通信方式三、总线的信息传输方式四、总线

11、使用权分配中国科学技术大学电子工程与信息科学系231、同步通信方式通信双方由统一时标控制数据传送。时标通常由CPU的总线控制部件发出,送到总线 上的所有部件;也可以由每个部件各自的时序发生器发出,但是必须由总线控制部件发出的时钟信号对它们进行同步。J/优点:模块间的配合简单一致;缺点:主从模须按速度最慢时间配合属强制性同步,必来设计公共时钟。中国科学技术大学电子工程与信息科学系24例1:读命令,其传输周期为:T1:主模块发地址总线读周期T2:主模块发读命令时钟T3:从模块提供数据地址T4:主模块撤销读命令读命令数据dataT1T2T3T4中国科学技术大学电子工程与信息科学系例2:写命令,其传输

12、周期为:主模块发地址T1.5:主模块提供数据25:主模块发写命令,从模块必须在规定时间内总线写周期T1T2T3T4将数据写入地址总线所指明的单元中。:主模块撤销写命令和数据等信号。时钟地址数据data写命令中国科学技术大学电子工程与信息科学系262、异步通信方式异步通信方式允许各模块速度的不一致性,给设计者充分的灵活性和选择余地。异步通信方式没有公共的时钟标准,而是采用应答方式(又称握手方式):主设备在发数据STB的同时发选通信号STB,从设备收到数据后应答ACK;主从模块之间增加两条握手应答线。ACK读/写地址数据I/O接口CPU中国科学技术大学电子工程与信息科学系27异步通信方式的三种握手

13、方式1)不互锁方式主设备发STB,告诉从设备当前数据有效。间隔固定时间后,认为从设备已经收到,撤销STB;从设备收到数据后发ACK应答。间隔固定时间后,撤销ACK。DATA不互锁方式应答时序图STBACK中国科学技术大学电子工程与信息科学系282)半互锁方式主设备发STB后,等待从设备的ACK应答。只有收到ACK后才撤销STB;从设备发ACK后,不等待主设备的应答。在间隔固定时间后,撤销ACK。DATA半互锁方式应答时序图STBACK中国科学技术大学电子工程与信息科学系293)全互锁方式(四边沿协议)主设备发STB后,等待从设备的ACK应答。只有收到ACK后才撤销STB;从设备发ACK后,等待

14、主设备的应答(撤销STB),然后才撤销ACK。主从设备相互等待,传输可靠性最高。DATA全互锁方式应答时序图STBACK中国科学技术大学电子工程与信息科学系30关于同步和异步通信方式的几点讨论:传输速度同步:异步:应答过程中的交互次数越多,速度越慢。可靠性最可靠的方式:异步全互锁。全互锁也会有不可靠的隐患?!互锁方式应配合使用等待超时处理机制。思考:怎样能够兼顾传输速度和通信的可靠性?中国科学技术大学电子工程与信息科学系313、半同步通信方式对于大多数的传送对象,均按照同步方式定时。如果系统中还有少数从设备速度较慢,增加一条Ready/wait状态信号线,慢速设备可以利用该状态信号线请求主模块

15、延长传送周期。例如:8086/808CPU、823ADMAC均采用半同步总线。当检测到READY信号线被拉低,则在T3/T4之间插入Tw,或者在S3/S4之间插入Sw。中国科学技术大学电子工程与信息科学系32半同步方式数据传输时序中国科学技术大学电子工程与信息科学系33半同步通信方式的特点J 集同步与异不是太高,各类设备的通信之优点,适用于系统工作速度又包含了许多工作速度差异较大的单系统。J 控制方式比异步通信简单,可靠性介于同步方式与异步方式之间。/ 缺点是系统时钟频率系统工作的速度还是太高,故从整体上看,。思考:怎样进一步提高总线利用率和加快总线的传输速度?中国科学技术大学电子工程与信息科

16、学系344、分离式总线通信方式在上述各种传输过程中,占用总线使用权的主设备以及被其选中的从设备,无论是否进行数据传输,始终占据着总线资源。若对读命令过程的进一步分析:在读命令传输周期中,除了申请总线这一阶段外,其余时间主要被用于如下三个方面的开销:(1) 主模块通过总线向从模块发送地址和命令;(2) 从模块按照命令进行读数据的必要准备;(3) 从模块经总线向主模块提供数据。中国科学技术大学电子工程与信息科学系分离式总线的基本思想:将一个传输周期(或总 线周期)分解为两个子周期。在第一个子周期中,主模块A获得总线使用权后,35将命令、地址、A模块的编号等其它信息发到系统总线上,由相关的从模块B接

17、收下来。然后A模块放弃总线,供其它模块使用。在第二个子周期中,B模块根据所收到的命令,经过一系列的内部操作,将A模块所需的数据准备 好,然后由B模块申请总线使用权,一旦获准,B模块将A模块的编号和所需数据、B模块的地址等信息送到总线上,供A模块接收。中国科学技术大学电子工程与信息科学系36分离式总线通信方式的特点:各模块欲使用总线都必须提出申请。在得到总线使用权后,主模块先在规定的时间内向对方传送信息,采用同步方式传送,不再等待对方的回答信号。各模块在准备数据传送的过程中都不占用总线,使总线可接受其它模块的请求。总线在被占用期间,都在进行有效工作。中国科学技术大学电子工程与信息科学系376B

18、2 总线原理一、总线的结构二、同步和异步通信方式三、总线的信息传输方式四、总线使用权分配中国科学技术大学电子工程与信息科学系38信息传输方式的分类:. 串行和并行传输. 信号(Signal)传输和消息(Message)传输. 单字节传输和突发传输(burstmode)单字节传输方式:在一个传输周期内,一般是先给出地址,然后给出数据。在其后的传输周期里,不断重复这种先送地址、后送数据的方式进行传输。突发传输方式:在传输大批量地址连续的数据时,第一个周期先送首地址,然后再给出数据;而在以后的传输周期内,接收端自动完成地址指针修正,发送端只需直 接传送数据,从而提高了总线的数据传送速率。中国科学技术

19、大学电子工程与信息科学系396B 2 总线原理一、总线的结构二、同步和异步通信方式三、总线的信息传输方式四、总线使用权分配中国科学技术大学电子工程与信息科学系40总线的使用权分配即总线判优控制,也称为总线使用权仲裁;总线使用权仲裁:多个主设备同时申请总线 时,按一定的优先等级顺序,判定哪个主设备 能优先使用总线。两种仲裁方式:集中式:将控制逻辑(即总线仲裁器arbitrator) 集中在一处 ,分为链式轮询、计数器轮询、独立请求 。分布式:将控制逻辑分散在(与总线连接的)各个 部件或设备上,由各个节点竞争使用权。中国科学技术大学电子工程与信息科学系41集中式总线判优控制举例(I)菊花链轮询方式

20、(Daiy Chain)数据线地址线总线忙BS总线请求BR总线控制器模块0模块1模块n总线允许BG总线允许BG总线允许BG中国科学技术大学电子工程与信息科学系42链式轮询方式的主要特点:越靠近器的模,优先级越高;链形优先级存在传播延迟,这种延迟与模块数量成正比,所以判优速度(几个)模块;慢,一般只能接少量的链形结构可靠性低条“链”失效;一个模块有故障就会造成整结构简单,造价较低。应用实例:IntMultiBus和Motorola VME总线中所使用串行仲裁均采用链式轮询方式。中国科学技术大学电子工程与信息科学系43集中式总线判优控制举例(II)独立请求方式(并行请求方式)数据线地址线BGnBR

21、n总线控制器BG1BR1BG0BR0模块0模块1模块nBUSY中国科学技术大学电子工程与信息科学系44独立请求方式的工作原理:每个模块有一条总线请求(BR)、一条总线允许(BG)和一条所有模块共用的总线忙(BUSY)信号;控制器内置一个优先级编码器和优先级译码器,用以选择优先级最高的请求,并产生出相应的“总线允许”信号;当BUSY信号有效时,表示有模块正使用总线,因此请求使用总线的模块必须等待,直至BUSY信号变为无效。所有需要使用总线的模块都可发“总线请求”信号,总线仲裁器仅向优先级最高的模块发出“总线允许”信号。独立请求方式的主要特点:判优速度快,且与模块数无关;所需“请求线”和“允许线”

22、较多,N个模块需要2N条。应用实例:MultiBus中使用的并行仲裁中国科学技术大学电子工程与信息科学系45分布式总线判优控制举例(I)自举分布式仲裁特点:使用多个请求线,不需要中心裁决器,每个设备独立地决定自己是否是最高优先级请求者。原理:分为申请期和裁决期。在申请期需要请求总线控制权的设备在各自对应的总线请求线上送出请求信号。在裁决期,每个设备将有关请求线上的合成信号取回分析,以确定自己能否拥有总线控制权。每个设备通过取回的合成信息能够检测出其它设备是否发出了总线请求。如果检测到其它优先级更高的设备也请求使用总线,则本设备暂时不能使用总线;否则,本设备就可立即使用总线。中国科学技术大学电子

23、工程与信息科学系46自举分布式仲裁原理图假定模块03通过BR03进行自举分布式仲裁。其中BR0为总线忙信号,正在使用总线的模块应将BR0置为有效;BRi为模 块i的总线请求信号线,只有在BR0无效时才能发总线请求。下图中模块0的优先级最低,模块3的优先级最高。Why?BR0(BUSY)BR1B2B3应用实例:NuBus(Macintoshi II中的底板式总线)和SCSI总线模块3模块2模块1模块0中国科学技术大学电子工程与信息科学系47分布式总线判优控制举例(II)冲突检测分布式仲裁基本思想:每个设备独立地请求总线。肯定会出现有多个设备同时使用总线的局面,造成冲突。当冲突被检测到后,冲突各方

24、可按照事先约定的某种策略, 选举一个设备并让其先使用总线。应用实例:Ethernet总线仲裁方案(CSMA/CD-Carri r Sen e Multip e Access- Collisi n Detect)先听后讲边讲边听随机重发若监听到冲突,则立即停止发送。随机等待一段时间后再重新尝试中国科学技术大学电子工程与信息科学系48内容6B 1 总线的概念6B 2 总线原理6B-3 微机系的内总线标准一、从PC/XTO Channl 到EISA二、局部总线:从VISA到PCI-Express6B 4 几种常用的外总线标准一、通用串行总线USB三、IDE和EIDE简介二、IEEE1394总线简介四

25、、SCSI总线简介中国科学技术大学电子工程与信息科学系496B 3 微机系统中的内总线标准应用于微机系统中的总线标准不断发展和演变, 其中比较著名或曾产生一定影响的总线标准有:S100Motoro a VME在微机中最早使用的总线,由业余爱好者设计;其优良的结构被许多后续的总线标准继承和引用;Intl MultiBusIntel为8086CPU开发的,曾经用于工业控制微机;Zilog Z-Bus8位机时代应用最广泛的微机总线;IIM PC/ TO Channel常被恭维成IM PC/XT总线;A 总线源自AT总线,16位,至今仍然能够见到;EISA总线ISA上加盖的“二层楼”,32位,曾用于P

26、C服务器;PI 总线目前广泛应用,有33MHz和66MHz及32位和64位之分。中国科学技术大学电子工程与信息科学系50一、从PC/XT机的 O Chann1)PC机系统总线早期发展历程l 到EISA20世纪80年代初期,IBM能扩展插槽”的结构,并定宽度的IO接口(虽然业界C/XT机中采用“主板”“功了总共62条信号线、8位数上“尊称”其为XT总线,但IBM始终低调地称之为 O channel)。其后,IBM又推出了采用Intl 8026 CPU的PC/AT微机系统,并定义了与XT总线兼容的16位的AT总线。1988年,除IBM以外的美国9大PC制造厂商,共同制定了基于AT总线的ISA总线(

27、Industril Standa dArchitecture),以及32位的EISA总线标准。中国科学技术大学电子工程与信息科学系512)PC/XT机的 O channel(XT总线)62线该62插槽和插卡结构。的长插口用双列插板连接,分A面(元件面)和B面(焊接面),每面有31条引脚(金手指),如下页图所示。62条信号线分为5类:8位数据线、20位地址线、控制线、时钟与复线以及电源地线。62条信号线分别介绍如下中国科学技术大学电子工程与信息科学系52O channel引脚布局示意图A为元件面B为背面COMPUTR FRONTCOMPUTR REAR中国科学技术大学电子工程与信息科学系53A、

28、数据线(8条)A2A9:8位数据线D0D7,双向、三态。B、地址线(20条)A12A31:20位的地址线A19A0,输出、三态。访问IO时仅有A15A0有效。C、控制线(23条)A1:I/O通道检查信号I OH CK,输入、低电平有效。该信号有效时表示系统板上存储器或I/O通道上奇/偶校验出错。它有效时将产生一次不可屏蔽中断(NMI中断)。A10:I/O通道就绪信号I OH RDY,输入、低有效。慢速设备可以通过使此信号为低电平来使CPU或DMA控制器插入等待周期,从而延长总线周期。中国科学技术大学电子工程与信息科学系A11:地址允许信号AEN,输出、高电平有效。由DMA 控制器8237产生,

29、此信号用来切断CPU控制,而允许DMA传送。54B8:插件板选中信号CALCTD,输入、高电平有I/O扩展槽中的扩展板B8引脚提供,该信号效。有效第表 第8个I/O扩展槽中的扩展板被选中。B11:存储器写命令MEMW,出、三态、低电平有效。B12:存储器读命令MEMR,输出、三态、低电平有效。B13:I/O写命令IOW,输出、三态、低电平有效。B14:I/O读命令IOR,输出、三态、低电平有效。中国科学技术大学电子工程与信息科学系B19: DACK0,输出、低电平有效。在XT机中,实际55上就是DRAM的刷新信号REFRESH,由DMA控制器产生,有效时表示系统响应了存储器的刷新请求。B4、B

30、21B25:中断申请信号IRQ2,IRQ3IRQ7, 输入、上升沿有效。来自I/O设备的中断申请信号,经 系统板上的中断控制器8259A送给CPU,其中IRQ2优 先级最高,IRQ7最低。B16、B6、B18:DMA请求信号DRQ1DRQ3,输入线、高电平有效,来自外设的DMA请求送往DMA控制 器8237。DRQ1优先级最高,DRQ3最低。B15、B26、B17:DMA通道13响应信号DACKDACK3,输出、低电平有效。由DMA控制器8237产生送往I/O接口,用来响应外设的DMA请求。中国科学技术大学电子工程与信息科学系B27:计数结束信号T/C,输出、正脉冲。当DMA控制 器8237计

31、数到0时,从T/C线上输出一正脉冲,通知外设,DMA传送结束。B28:地址锁存允许信号ALE,输出、下降沿有效。该 信号由总线控制器8288产生,在其下降沿将CPU送出的地址A19A0锁入地址锁存器。. 时钟与复位线(3条)56B2:系统总清信号REST DRV,输出、高电平有效。该信号有效,使系统各部件复位。B20:系统时钟信号CLK,输出。PC/XT中该信号由OSC信号经8284时钟发生器三分频后得到,频率为4.77MHz,时钟周期为210ns;在ISA中为频率为8MHz的系统时钟。中国科学技术大学电子工程与信息科学系B30:晶振信号OSC,频率为14.31818MHz,周期为70ns。5

32、7. 电源与地线(8条)B3,B29:+5VB5:-5V B7:-12V B9:+12VB1,B10,B31:GND中国科学技术大学电子工程与信息科学系PC和PC/XT总线的微机系统结构示58CU 8088(4.77MHz)8087(可)RM BISDRAM 控R M器823 定时/计扬829 中断控器8 个 8 位 62 引脚扩扩展总线82 0串行通信控器82 7 DMA 控DMA 页面寄键盘与并行控制器中国科学技术大学电子工程与信息科学系593)16位 ISA总线(AT总线)为保证16位的ISA总线与PC总线的兼容,ISA总线的插座结构中在原PC总线62芯插座的基础上又 增加了一个36线插

33、座,即同一轴线上的总线插槽分为62线和36线两段,共98线。ISA不仅增加了数据带宽和地址总线的数量,而且在保证与XT总线兼容的前提下,对原来XT总线的部分信号重新进行了定义。ISA引脚信号见教材P252图6-13。中国科学技术大学电子工程与信息科学系ISA总线插槽ISA总线插槽有一长一短两个插口; 长插口基本上是XT总线的继承;60短插口有36个引脚,以C18C1和D18D1表示,也分别列于插槽的两面,短插口是对XT总线的扩充。C1A1A31C18外内B31D110.16B1D182.54138.5mm总线新增加的条信号线ISA3661中国科学技术大学电子工程与信息科学系ISA总线不仅增加了

34、数据带宽和地址总线数量,而且重新定义了原有XT总线的信号线,使得ISA总线有了内总线的基本雏形62ISA总线作频率为8MHz,24根地址线,16位数据线,拥有大量的功能丰富的接口卡。虽然其最大传输速率只有16MB/s,但是从286到Pentium,历经几代微机.ISA问世后的十多年间,大多数PC机主板上都带有34个ISA总线插槽,即可以插入8位ISA卡(XT总线),又可以插入16位ISA ISA插槽的P由于ISA总直到最近,仍有少数厂家仍然生产带有。自XT总线,受累于XT总线的先天不足,管在制定ISA总线标准时做出了很大努力,在技术上ISA 仍然无法与当时的VME和MultiBus等总线相比。

35、思考:为什么ISA总线在PC机独领风骚十数年?中国科学技术大学电子工程与信息科学系ISA总线对原来8位 O Channel的改动部分:63虽然名称没变,但传输方向发生变化。 O Channel中这两个信号的方向是输出,意味着只允许主板上的主设备访问插槽上的从设备。在ISA中,这两条信号线变成了双向,表C : IIS: IOWB13脚C : IORI A : IORB14脚明ISA总线允许插卡上的主设备访问主板上的资源。中国科学技术大学电子工程与信息科学系在36芯插座上,ISA扩展和重新定义的部分信号因为有24位地址信号,允许最大存储容量是16M。64其中:1)SA190的传送方向由原来的单向输

36、出(从主板到插卡)改为双向,意味着允许插卡上可以有主控设备,插卡上的主控设备可以控制系统总线;2)LA23LA17(其中有3条与需要使用这部分地址信号的插卡9A17重叠)在主板上没有锁存,自行锁存(利用BALE信号)。SD15SD0:16位数据信号中国科学技术大学电子工程与信息科学系65SBHE:总线高字节允许IRQ15、IRQ14、IRQ12、IRQ11、IRQ10AT机以后的PC机上使用了2片中断控制器8259A(主片和 从片),可有15级中断请求。另外三条DMA请求/响应线AT机以后的PC机中使用了2片DM片),共有7个DMA通道。C 8237A(1主片1从DRQ7DR5 、DRDRQ0

37、:DMA请求信号。CK3DACK0:DMA请求响应。DACK7DACK5、中国科学技术大学电子工程与信息科学系66存储器读/写信号在扩展短槽上,传输方向为双向I/O。在原来长槽上,传输方向仍然为单向输出16位访问周期信号有效时表示当前传送的是16位总线周期总线主控当DMA控制器或者其它主控设备使用总线期间,为低电平有什么意义?中国科学技术大学电子工程与信息科学系ISA系统结构示例基于80486的PC机67CPU80486DRAM 与 L22 Cache128K 512K主存 DRAM4768M BCPU总线Cace控制器SIMM C AT/ISA 核心逻辑芯片组内含: 7 个 DM A 通道1

38、5 级中断时间/计数器总线缓冲器扩展总线控制器8042M PUKBD/M ous控制器8位总线实时时钟/日历后备电池CM RAM8 个 8 位XT 插槽64K128KRM BIOSISA 总线PC/AT 或 ISA 插616 位个AT/ISA 扩槽中国科学技术大学电子工程与信息科学系684)MCA总线随着80386、80486的问世,ISA的弱点逐渐显现。 例如:24位地址线以及16位数据线与32位CPU不匹配,传输速率低,不支持自动配置,不支持总线主控技术及缺乏对多处理器的支持等。为解决上述问题,IBM所采取的策略是推出一种全新的MCAMic o Channl Architecture(微通

39、道结构)总线。其特点是:将数据线和地址线都扩展为标准的32位扩展总线系统,系统的寻址范围增加到4GB,传输速率可以达到40MB/s。中国科学技术大学电子工程与信息科学系MCA优点很多,例如:MCA具有多总线功能;有总线仲裁机构,支持多处理器; 可支持多任务处理,具有并行处理能力;具有附加卡定义档案,易于机器识别和系统诊 断;具有可编程任选机制,可自动进行系统配置和安装。MCA总线有许多优于传统的设计,增加了许多新的特殊的功能,有些功能甚至连现在最新的PCI总线都不具备。69但是为什么MCA总线很少得到应用?MCA的失败不是技术层面上的原因,而是由于IBM在“不恰 当的时候提出了不恰当战略”。/

40、 首先是MCA与当时已广泛使用的ISA总线不兼容,缺少最终用户的支持;/ 其次IBM公司为MCA注册了版权,可观的版权费使得许多厂家望而却步,又失去了生产厂商的支持。中国科学技术大学电子工程与信息科学系705)EISA总线为了大力推广MCA总线,IBM公司于1988年9月宣布将于1989年全面停产基于AT总线的PC机,转而生产基于MCA总线的PS(个人系统)机,很快IBM为自己 的轻率之举付出了代价。Compaq,HP,AST,Epson,NEC等九家计算机公 司立即抓住这一机会,高举保护用户以往投资的“义 旗”,宣布今后将继续大量生产基于ISA总线(与AT总 线几乎完全相同并100兼容)的P

41、C机。同时,针对ISA总线的不足,九家公司选择了另外一 策略,联合推出一种与ISA兼容的总线标准,称为扩的工业标准体系结构EISA(Extend Standa d Architecture)。d Indust y中国科学技术大学电子工程与信息科学系EISA不仅与ISA兼容,在许多方面还参考了MCA的设计,并且EISA标准是开放的,因此受到了众多生 产厂家和广大用户的欢迎。大量的基于EISA总线的 服务器、工作站以及插卡(网卡、SCSI卡、图形图 像卡等)纷纷涌现。EISA总线的主要特点是:J 支持新一代智能总线主控技术,使总线上的功能插卡可以控制系统总线;J 可以实现32位内存寻址,实现对CP

42、U、DMA和总线控制器的32位数据传送;J 支持突发式(Burst)传输访问模式,峰值数据传输速率为32MB/s;J 支持电子触发中断方式、多处理器和自动配置等。71中国科学技术大学电子工程与信息科学系EISA适合于对总线使用要求较高的系统软件,例如Windows,Unix(X11)和OS/2等带有GUI的操作系统;也适用于要求数据传输速率较高及数据传输量 较大的应用场合,如:高速图形图像处理、LAN管理和文件服务应用软件等。72正是由于EISA保持了与ISA总线的兼容性,保护了用户已在ISA总线微机硬件和软件上的巨大投资。因而得到的用户的青睐。为了保持与ISA标准兼容,EISA总线槽的物理尺寸与ISA相同。为了增加引脚,EISA采用了纵向加高(

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 国际注册内部审计师(CIA)资格考试(内部审计知识要素)试题库及答案 (西藏2025年)

- 2025年国际注册信息系统审计师(CISA)资格考试(英文版)仿真试题及答案一

- 2025股权转让居间服务合同范本

- smtp协议书源代码

- 签订协议书 翻译

- 乡镇招商引资协议书

- 无偿扶持协议书

- 资金 技术合作协议书

- 高管期权协议书

- 2025年短视频创作者内容合作合同协议

- 上海世博会视觉识别VI手册-VI设计-清晰完整课件

- NPI试产管理控制程序文件

- 氯化镉-理化性质及危险特性表

- 深刻认识铸牢中华民族共同体意识PPT铸牢中华民族共同体意识促进各民族交往交流交融PPT课件(带内容)

- GB/T 18983-2017淬火-回火弹簧钢丝

- GB 30080-2013铜及铜合金熔铸安全生产规范

- 北京师大附中2022学年上学期初中七年级期中考仿真试政治试卷1

- 道德与法治《我学习,我快乐》评课稿

- 沉默的螺旋课件

- 成都钢琴谱乐谱

- ABB变频器ACS510说明书

评论

0/150

提交评论