下载本文档

版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

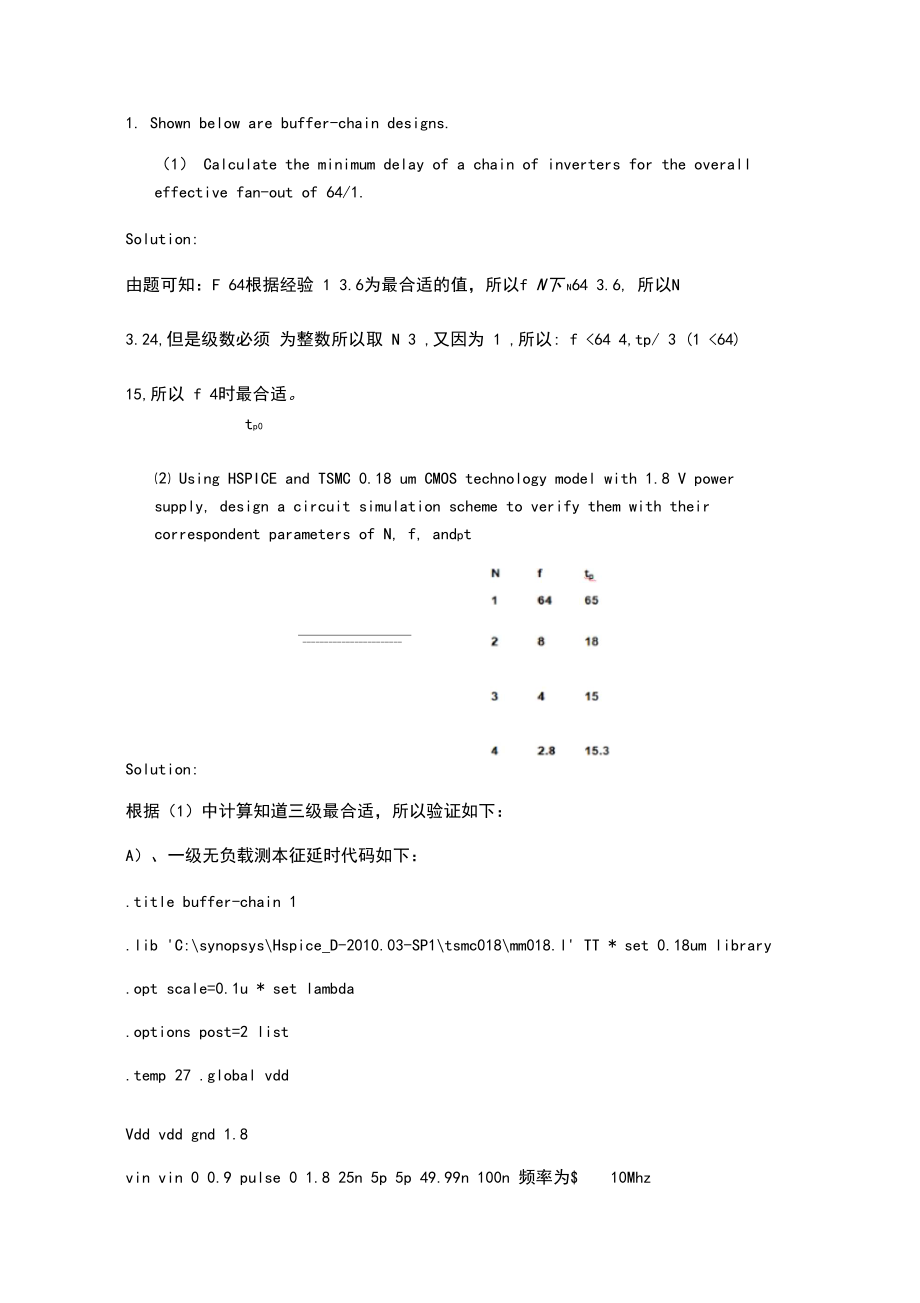

1、1. Shown below are buffer-chain designs.(1) Calculate the minimum delay of a chain of inverters for the overall effective fan-out of 64/1.Solution:由题可知:F 64根据经验 1 3.6为最合适的值,所以f N下 N64 3.6, 所以N 3.24,但是级数必须 为整数所以取 N 3 ,又因为 1 ,所以: f <64 4,tp/ 3 (1 <64) 15,所以 f 4时最合适。tp0 Using HSPICE and TSMC 0.18

2、 um CMOS technology model with 1.8 V power supply, design a circuit simulation scheme to verify them with their correspondent parameters of N, f, andptSolution:根据(1)中计算知道三级最合适,所以验证如下:A)、一级无负载测本征延时代码如下:.title buffer-chain 1.lib 'C:synopsysHspice_D-2010.03-SP1tsmc018mm018.l' TT * set 0.18um li

3、brary.opt scale=0.1u * set lambda.options post=2 list.temp 27 .global vddVdd vdd gnd 1.8vin vin 0 0.9 pulse 0 1.8 25n 5p 5p 49.99n 100n 频率为$10MhzCl vout gnd 0f $Cg1=2.46fF,负载为 CL=157.44fF.subckt inv in out wn=3.5 wp=10 t=7.5mn out in gnd gnd NCH l=2 w=wn ad='wn*t' pd='wn+2*t' as='

4、;wn*t' ps='wn+2*t'mp out in vdd vdd PCH l=2 w=wp ad='wp*t' pd='wp+2*t' as='wp*t' ps='wp+2*t' .endsX1 vin vout inv wn=3.5 wp=10 t=7.5.op.tran 5p 5n.meas tran voutmax max v(vout) from=5p to=5n.meas tran voutmin min v(vout) from=5p to=5n$一级.meas tran tphl1+tr

5、ig v(vin)+val=0.9+rise=1+targ v(vout)+val='0.5*(voutmax-voutmin)+voutmin'+fall=1.meas tran tplh1+trig v(vin)+val=0.9+fall=1 +targ v(vout)+val='0.5*(voutmax-voutmin)+voutmin'+rise=1.end1) 一级无负载测得本征延时约为17ps;$DATA1 SOURCE-, HSPICEJ VERSION=,D-2010. 03Tpi 32-B1T7,TITLE J .title buffer-ch

6、ain 1'voutinaKvoutinintphlltplhlteinperal t er#2. 2321-S 24721.725e-U k 703e-ll.27- 000012)带上64倍Cg1大小的负载测得延时为750.35ps,是本征延时的44倍$DATA1 SOURC拉'HSPICE' VERSION D-2010.03-SF1 32-BIT'TITLE J title buffer-chainvoutmaxvoutmintphlltplhltsinperalter#1. S083T, 476-031. 059e-107. 94叫TO27,00001B

7、)、三级带负载测延时代码如下: .title buffer-chain 3 .lib 'C:synopsysHspice_D-2010.03-SP1tsmc018mm018.l' TT * set 0.18um library.opt scale=0.1u * set lambda.options post=2 list.temp 27.global vdd.param fan=4Vdd vdd gnd 1.8vin vin 0 0.9 pulse 0 1.8 25n 5p 5p 49.99n 100nCl vout gnd 0f $Cg1=2.46fF,负载为 CL=157.

8、44fF.subckt inv in out wn=3.5 wp=10 t=7.5 mn out in gnd gnd NCH l=2 w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t' mp out in vdd vdd PCH l=2 w=wp ad='wp*t' pd='wp+2*t' as='wp*t' ps='wp+2*t' .endsX1 vin 2 inv wn=3.5 wp=10 t=7.5X2 23 in

9、v wn='fan*3.5' wp='fan*10' t=5X3 3 vout inv wn='fan*fan*3.5' wp='fan*fan*10' t=5.op.tran 50p 500n.meas tran voutmax max v(vout) from=50p to=500n.meas tran voutmin min v(vout) from=50p to=500n$三级.meas tran tphl3+trig v(vin)+val=0.9+rise=1+targ v(vout)+val='0.5*(vou

10、tmax-voutmin)+voutmin'+fall=1.meas tran tplh3+trig v(vin)+val=0.9+fall=1+targ v(vout)+val='0.5*(voutmax-voutmin)+voutmin'+rise=11)带上64倍Cg1大小的负载测得延时为174.6ps,是本征延时的10.27倍32-BIT1tplh31, 794e-10$ DAT Al SOURCE'' HSP1CE1 VERSION" D-2 01k 03-SPl.TITLE ' . title bufferchainvout

11、inaxiroutjpintphl3teipperalter#L 8449-6. U9e-021. 693e-102- 00001总结如下:经过调整参数近似时每一级的1 ,所以经过手工计算得到一级带负载和三级带负载的延时比值为:tp3 空收 0.2344,而仿真得到的结果为tp1 65tp0同理其他级的延时代码也是如上的旦立0.2327,所以符合手工计算的比值,750.35写法,经过仿真得到三级延时最小。.end2. Consider the logic network below, which may represent the critical path of a more complex

12、 logic block. The output of the network is loaded with a capacitance which is 5 times larger than the input capacitanceof the first gate, which is a minimum-sized inverter. The effective fanout of the path hence equals F = C/Cg1 =5.Using HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V power

13、 supply, design a circuit simulation scheme to verify the OPTIMAZATION parameters ofg, f, and s for each of the inverter and gates.Solution:由题得到路径逻辑努力 G 1 5 5 1 25 ,由于没有分支B=1 ,所以3 39H GFB卫5,所以使延时最小的逻辑努力为h N日4陛1.93,得到如下 9, 92.6的扇出系数:f1 1.93, f2 1.16, f3 1.16, f4 1.93,利用书上公式6.18计算得到尺寸系数 § 1,S2 f1

14、gl/g2 1.16,S3 f1f2gl/g3 1.34,s4f1f2f3gl/g4电路仿真代码如下:.title INV 2NAND 2NOR.lib 'C:synopsysHspice_D-2010.03-SP1tsmc018mm018.l' TT * set 0.18um library .options post=2 list.temp 27.global vddVdd vdd gnd 1.8vin vin 0 0.9 pulse 0.0 1.8 150p 5p 5p 290p 600pC1 vout gnd 12.3f $Cg1=2.46fF,所以负载为 12.3fF

15、.subckt inv1 in out wn=0.35u wp=1u t=0.75umn out in gnd gnd NCH l=0.2u w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t'mp out in vdd vdd PCH l=0.2u w=wp ad='wp*t' pd='wp+2*t' as='wp*t' ps='wp+2*t' .ends.subckt nand3 NAND-A1 NAND-D1 NAND

16、-B1 NAND-C1 wn='0.35u*1.16' wp='1u*1.16't=0.5u $优化尺寸系数S2*.subckt nand3 NAND-A1 NAND-D1 NAND-B1 NAND-C1 wn=0.35u wp=1ut=0.5u$未优化尺寸系数S2mn3 NAND-S2 NAND-C1 gnd gnd NCH l=0.2u w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t'mn2 NAND-S1 NAND-B1 NAND-S2 gnd

17、NCH l=0.2u w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t'mn1 NAND-D1 NAND-A1 NAND-S1 gnd NCH l=0.2u w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t'mp1 NAND-D1 NAND-A1 vdd vdd PCH l=0.2u w=wp ad='wp*t' pd='wp+2*t' as=&

18、#39;wp*t' ps='wp+2*t'vdd PCH l=0.2u w=wp ad='wp*t' pd='wp+2*t'mp2 NAND-D1 NAND-B1 vdd as='wp*t' ps='wp+2*t'vdd PCH l=0.2u w=wp ad='wp*t' pd='wp+2*t'mp3 NAND-D1 NAND-C1 vdd as='wp*t' ps='wp+2*t'.ends .subckt nor2 NOR-A1 NOR-D

19、1 NOR-B1 wn='0.35u*1.34' wp='1u*1.34' t=0.5u$优化尺寸系数S3t=0.5u*.subckt nor2 NOR-A1 NOR-D1 NOR-B1 wn=0.35u wp=1u$未优化尺寸系数S3mn2 NOR-D1 NOR-B1 gnd as='wn*t' ps='wn+2*t'mn1 NOR-D1 NOR-A1 gnd as='wn*t' ps='wn+2*t'mp1 NOR-S1 NOR-A1 vdd as='wp*t' ps='

20、wp+2*t'gnd NCH l=0.2u w=wn ad='wn*t' pd='wn+2*t'gnd NCH l=0.2u w=wn ad='wn*t' pd='wn+2*t'vddPCH l=0.2u w=wp ad='wp*t' pd='wp+2*t'mp2 NOR-D1 NOR-B1 as='wp*t' ps='wp+2*t'NOR-S1 vdd PCH l=0.2u w=wp ad='wp*t' pd='wp+2*t'

21、.ends.subckt inv2 in out wn='0.35u*2.6' wp='1u*2.6' t=0.5u$优化尺寸系数S4*.subckt inv2 in out wn=0.35u wp=1u t=0.5u$未优化尺寸系数S4mn out in gnd gnd NCH l=0.2u w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t'mp out in vdd vdd PCH l=0.2u w=wp ad='wp*t' pd=&

22、#39;wp+2*t' as='wp*t' ps='wp+2*t'.endsX1 vin 2inv1X2 23vdd vdd nand3X3 34gnd nor2X4 4 voutinv2.op.tran 5p 3000p.meas tran voutmax max v(vout) from=5p to=3000p.meas tran voutmin min v(vout) from=5p to=3000p.meas tran tphl+trig v(vin)+val=0.9+rise=2+targ v(vout)+val='0.5*(voutmax-voutmin)+voutmin'+rise=2.m

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025年消费者购买力对美容美发行业影响可行性报告

- 2025年环保型塑料替代品研发与市场前景可行性研究报告

- 2025年企业内部员工绩效管理分析可行性研究报告

- 2025年环保型塑料产品性能与替代传统材料可行性分析报告

- 虫洞能量传输系统优化施工方案

- 集成学习在物联网安全中的应用-洞察及研究

- 维修流程优化与自动化-洞察及研究

- 工业通信协议安全-洞察及研究

- 太空环境监测技术-洞察及研究

- 交通智能化系统建设的规划与实施方案

- 终身教育理念课件

- DB37-T 4328-2021 建筑消防设施维护保养技术规程

- 《中小企业划型标准规定》补充说明

- 《消防安全技术实务》课本完整版

- 人教A版高中数学选择性必修一全册质量检测【含答案】

- 深水质表59沟(渠)清淤单元工程施工质量验收评定表

- DB32-T 3129-2016适合机械化作业的单体钢架塑料大棚 技术规范-(高清现行)

- 林业政策法规考试题库(含答案)

- 家具设计与陈设6家具与室内陈设设计课件

- 《汽车文化》教案(全)

- 门式轻钢之结构支撑体系(PPT30页)

评论

0/150

提交评论