下载本文档

版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、第3章逻辑代数及逻辑门3-1 填空1、与模拟信号相比,数字信号的特点是它的离散性。一个数字信号只有两处值分别表不'为0和1 。2、布尔代数中有三种最基本运算:与、或和非,在此基础上又派生出五种基本运算,分别为与非、或非、异或、同或和与或非。3、与运算的法则可概述为:有0"出 0,全1"出;类似地或运算的法则为有“ 1出“ 1”全“叱“ 0" 。4、摩根定理表示为:AB= A + B ; A + B= A B o5、函数表达式Y= AB +C + D ,则其对偶式为 Y*=(A+B)C-D o6、根据反演规则,若丫= AB+C + D +C,则Y = (AB

2、+C + D)-C 。7、指出下列各式中哪些是四变量A B C D 的最小项和最大项。在最小项后的()里填入mi,在最大项后的()里填入Mi,其它填x (i为最小项或最大项的序号 )。(1) A+B+ D (X);(2) ABCD (m7 );(3) ABC (X)(4)AB(C+ D) (X);(5) A + B + C + D (M 9 ) ; (6) A+B+CD (X );8、函数式F=AB+BC+CD 写成最小项之和的形式结果应为Z m(3,6,7,11,12,13,14,15),写成最大项之积的形式结果应为口 M ( 0,1,2,4,5,8,9,10 )9、对逻辑运算判断下述说法是

3、否正确,正确者在其后()内打对号,反之打X。(1)若 X+Y=X+Z,则 Y=Z ; ( X )(2) 若 XY=XZ ,则 Y=Z ; ( X )(3) 若 X® Y=X ® Z,则Y=Z; (V)3-2】用代数法化简下列各式(1) Fi = ABC AB =1(3) F3 = AC ABC ACD CD=A CD(2) F2 = ABCD ABD ACD = AD3-3】用卡诺图化简下列各式(1) F1 = BC AB ABC =AB C F3 =AC AC BC BC (4) =AB AC BC或 Ab AC BC(5) F5 = ABC AC ABD (6) =aB

4、 AC Bd(2) F2 = AB BC BC=A BF4 = ABC ABD ACD CD ABC AcD =A D-AB CD ABC AD aBc=a Bc CD(8) F8 = aC Ac Bd bD=ABCD AbcdaBcd abcdF7 = AC AB BCD BD ABD ABCD=A BD BD(4) F4 = A B C (A B C) (A B C)=A BC(9) F9 = A(C 二 D) BCD ACD ABCD =CD CD(10)F1o= F10=AC AB BCD BEC DEC =AB AC BD EC3-4】用卡诺图化简下列各式(1) P1(A,B,C尸、

5、m(0,1,2,5,6,7) = AB AC BC(2) P2(A,B,C,D)= '、m(0,1,2,3,4,6,7,8,9,10,11,14) = Ac AD B CDP3(A,B,C,D尸、m(0,1,4,6,8,9,10,12,13,14,15) = AB BC aD bD(4) P4 (A,B,C,D)= M1 *M7 A BC BC D3-5】用卡诺图化简下列带有约束条件的逻辑函数 R(A,B,C,D )=£ m(3,6,8,9,11,12)+£ d(0,1,2,13,14,15) = aC+BD + BCD(或AcD)(2) P2(A,BA,D)=v

6、m(0,2,3,4,5,6,11,12) % d(8,9,10,13,14,15) = BC BC D(3) P3 = A +C +D + ABCD + ABCD = AD + ACD + BCD (或ABD)AB+ AC=0(4) P4 = ABCD ABCD = A B(A B C D为互相排斥的一组变量,即在任何情况下它们之中不可能两个同时为1)3-6 】 已知:Yi = AB + AC + BDY2 = ABCD + ACD + BCD + BC用卡诺图分别求出 Y1M , Y + Y2,Y 6 Y2。解:先画出Yi和丫2的卡诺图,根据与、或和异或运算规则直接画出YY2 ,Yi+y2,

7、YiY2的卡诺图,再化简得到它们的逻辑表达式 :Yi 丫2 = ABD ABC CDY1 Y2 = AB C BDYi z Y2= ABCD ABC BCD ACD第4章集成门电路4-i 填空i .在数字电路中,稳态时三极管一般工作在心(放大,开关)状态。在图4.i中,若Ui<0,则晶体管邀上(截止,饱和),此时Uo= 3.7V (5V, 3.7V, 2.3V);欲使晶体 管处于饱和状态,Ui需满足的条件为 b ( a.Ui>0 ; b. Ui 0.7之削 c.Rb 凡Ui -0.7V。FT,在电路中其他参数不变的条件下,仅Rb减小时,晶体管的饱和程度加word资料可编辑途_ (减

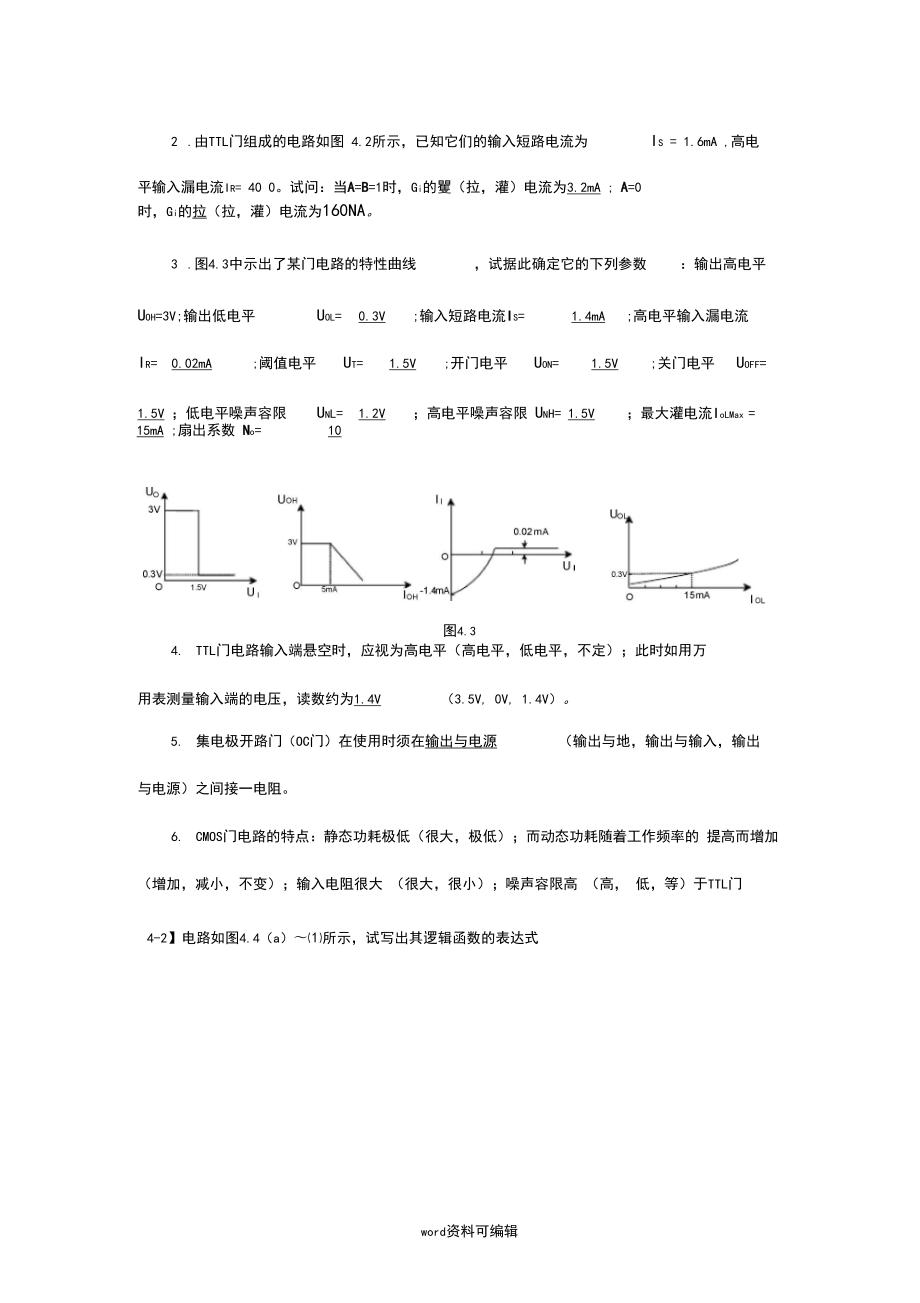

8、轻,加深,不变);仅Rc减小时,饱和程度 减轻(减轻,加深,不变)。图中C的作用是2 .由TTL门组成的电路如图 4.2所示,已知它们的输入短路电流为Is = 1.6mA ,高电平输入漏电流Ir= 40 0。试问:当A=B=1时,Gi的矍(拉,灌)电流为3.2mA ; A=0 时,Gi的拉(拉,灌)电流为160NA。3 .图4.3中示出了某门电路的特性曲线,试据此确定它的下列参数:输出高电平Uoh=3V;输出低电平Uol=0.3V;输入短路电流IS=1.4mA;高电平输入漏电流Ir=0.02mA;阈值电平Ut=1.5V;开门电平Uon=1.5V;关门电平Uoff=1.5V ;低电平噪声容限Un

9、L=1.2V;高电平噪声容限 UnH= 1.5V;最大灌电流loLMax =15mA ;扇出系数 No=10图4.34. TTL门电路输入端悬空时,应视为高电平(高电平,低电平,不定);此时如用万用表测量输入端的电压,读数约为1.4V(3.5V, 0V, 1.4V)。5. 集电极开路门(OC门)在使用时须在输出与电源(输出与地,输出与输入,输出与电源)之间接一电阻。6. CMOS门电路的特点:静态功耗极低(很大,极低);而动态功耗随着工作频率的 提高而增加 (增加,减小,不变);输入电阻很大 (很大,很小);噪声容限高 (高, 低,等)于TTL门4-2】电路如图4.4(a)所示,试写出其逻辑函

10、数的表达式CMOSTTLCMOS10kQ XAB r-100GX51c工F3TTL A B100kQ TF4CMOSTTL10k.i(d)(e)图4.4100k.i(f)解:(a) F1 =A (b) F2 =1(c) F3 = A B(d) F4 =A B (e) F5 =1(f)F6 = B(a)(b)4-3】图4.5中各电路中凡是能实现非功能的要打对号,否则打X。图(a)为TTL 门电路,图(b)为CMOS门电路。5V1M X(a)TG口 1Mx(b)图4.54-4】要实现图4.6中各TTL门电路输出端所示的逻辑关系各门电路的接法是否正确? 如不正确,请予更正。解:A B CF二A日B田

11、CF =AB CDX(b)图4.64-51TTL三态门电路如图4.7(a)所示,在图(b)所示输入波形的情况下,画出F端的波形。C(b)图4.7解:当 C=1 时,F =AB;当 C=0 时,F=AB = A + B。于是,逻辑表达式 F =ABC+(A +B)CF的波形见解图所示。4-6】图4.8所示电路中Gi为TTL三态门,G2为TTL与非门,万用表的内阻20k Q/V ,量程 5V。当C=1或C=0以及S通或断等不同情况下,Uoi和U02的电位各是多少?请填入表中,如果62的悬空的输入端改接至 0.3V,上述结果将有何变化?解:CS通S断1Uoi =1.4VU01 =0V1Uo2 =0.

12、3VU02 =0.3V0Uoi =3.6VU01 =3.6V0U02 =0.3VU02 =0.3V若G2的悬空的输入端接至0.3V,结果如下表CS通S断1U01 =0.3VU01 =0V1U02 =3.6VU02 =3.6V0U01 =3.6VU01 =3.6V0U02 =3.6VU02 =3.6V4-7】已知TTL逻辑门Uoh=3V, Uol=0.3V ,阈值电平Ut=1.4V ,试求图4.9电路中各电压表的读数。解:电压表读数 Vi=1.4V , V2=1.4V , V3=0.3V , V4=3V , V5=0.3V 。4-8如图4.10(a)所示CMOS电路, 画出F端的波形。已知各输入

13、波形A、B、C 如图(b)所示,R=10kC,请LTLl(b)解:当C=0时,输出端逻辑表达式为+ Ac。答案见下图。图 4.10F= A + B ;当 C=1 时,F = A,即,F = A + B C4-9】由CMOS传输门和反相器构成的电路如图4.11(a)所示,试画出在图(b)波形作用下的输出 Uo 的波形(Uii=10V Ui2=5V)UiiTGUoUl2TG输出波形见解图(a)图 4.11Uo*t(b)第5章组合数字电路5-1】分析图5.1所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。解: Y=ABC ABC ABC ABC=',m(0, 3, 5&

14、#169; A 二 B 二 C5-2】逻辑电路如图5.2所示:1 .写出S、C、P、L的函数表达式;2 .当取S和C作为电路的输出时,此电路的逻辑功能是什么?图5.25-2】解:1 . S =X 二 Y 二 ZC =X (Y 二 Z) YZ =XY XZ YZP =Y 二 ZL=YZ2 .当取S和C作为电路的输出时,此电路为全加器5-31图5.3是由3线/8线译码器74LS138和与非门构成的电路,试写出Pi和P2的表达式,列出真值表,说明其逻辑功能解:P =£ m(0,7) = ABC +ABC已=£ m(1,2,3,4,5,6) = AB+BC + AC 或 P2 =

15、AB + BC + AC5-4】图5.4是由八选一数据选择器构成的电路,试写出当GiGo为各种不同的取值时的输 出Y的表达式。解:结果如表A5.4所示。表 A5.4G1GoY00A01AB10AB11AB5-5】用与非门实现下列逻辑关系,要求电路最简。Pi =' m(11,12,13,14,15)IP2m(3,7,11,12,13,15)P3 -m(3,7,12,13,14,15)解:卡诺图化简如图 A5.5所示。P=AB+ACDP2 = ABC + ACD + ACD P3 = AB + ACD将上述函数表达式转换为与非式,可用与非门实现,图略。5-6】某水仓装有大小两台水泵排水,如

16、图5.6所示。试设计一个水泵启动、停止逻辑控制电路。具体要求是当水位在H以上时,大小水泵同时开动;水位在H、M之间时,只开大泵;水位在M、L之间时,只开小泵;水位在L以下时,停止排水。(列出真值表,写出 与或非型表达式,用与或非门实现,注意约束项的使用)L图5.6HM解:1.真值表如表A5.6所不;表 A5.6HMLF2F10000000101010XX01110100XX101XX110XX111113.表达式为F2 = MF1 = Ml H = MH LH或按虚线框化简可得F1 =HM +L。图略。5-7】仿照全加器设计一个全减器,被减数A,减数B,低位借位信号J0,差D, 的借位J,要求

17、:1 .列出真值表,写出D、J的表达式;2 .用二输入与非门实现;3 .用最小项译码器 74LS138实现;4 .用双四选一数据选择器实现 。解:1 .设被减数为A,减数为B,低位借位为Jo,差为D,借位为Jo列真值表如表向高位A5.7所示。表 A5.7ABJ0DJ0000000111010110110110010101001100011111化简可得D(A,B,Jo) =,m(1,2,4,7) =A二 B 二 J。« -工J(A,B,J0) =、m(1,2,3,7) = A二 B J0 AB2 .用二输入与非门实现的逻辑图见图A5.7(a)。3 .用74LS138实现的逻辑图见图

18、A5.7(b)。4 .用双四选一数据选择器实现的逻辑图见图A5.7(c)。图 A5.75-8】设计一组合数字电路,输入为四位二进制码 B3B2B1B0,当B3B2B1B0是BCD8421码时输出Y=1 ;否则Y=0。列出真值表,写出与或非型表达式,用集电极开路门实现。解:1 .根据题意直接填写函数卡诺图,如图A5.8(a)所示。化简为0的最小项,可得输出Y的与或非式Y = B3B2 &B2 .用集电极开路门实现的逻辑图见图A5.8(b)。解:0000111105-9】试用最小项译码器 74LS138和和一片74LS00实现逻辑函数P(AB)=" m(0,3)P2(A, B)八

19、 m(1,2,3)本题有多种答案,答案之一如图A5.10所示,其余答案请同学自行设计 P2J一上二Dp13图 A5.105-10试用集成四位全加器 74LS283和二输入与非门实现 BCD8421码至U BCD5421码的转换。解:将BCD8421码转换为BCD5421码时,则前五个数码不需改变,后五个数码需要加 3,如表A5.11所不'。表 A5.11被加数(BCD8421)加数和(BCD5421)A3AA1A0B3B2B1B0S3ssiS0000000000000000100000001001000000010001100000011010000000100010100111000

20、011000111001011100111010100000111011100100111100由表可得74LS283的加数低两位的卡诺图,见图A5.11(a)所示。设BCD8421码输入为DCBA,则化简可得B1= B0= D+CB+CA =D CB CA用74LS283和二输入与非门实现的逻辑图见图A5.11(b)。(a)(b)图 A5.115-11】设计一个多功能组合数字电路,实现表5.1所示逻辑功能。表中C1, Co为功能选择输入信号;A、B为输入变量;F为输出。1、列出真值表,写出F的表达式;2、用八选一数据选择器和门电路实现CiCoF00A+B01AB表5.1解:1 .输出F的表达

21、式为i ia© bF =C0AB C0AB C1AB C0AB C1c0AB2 .用八选一数据选择器和门电路实现逻辑图如图A5.12所示。图中D0= D3= D4= D7= B; D1 =1 ;D2=0 ; D5= D6= B图 A5.125-12】电路如图5.12(a)所示。1 .写出L, Q, G的表达式,列出真值表,说明它完成什么逻辑功能2 .用图5.12 (a)、(b)所示电路构成五位数码比较器£>Y A<B Y A=B Y A>B(A<B) i(A=B) i 74LS85(A>B) i(b)A3A2A1A0 B3B2B1B0(a)图

22、5.12解:1 .输出函数表达式为L = Ab G = AB Q = AB AB该电路为一位数码比较器 。2 .将一位数码比较器的输出L、Q、G接到74LS85的串行输入端即可。5-14】解:设合格为1”,通过为1” ;反之为0”。根据题意,列真值表见表 A5.14。表 A5.14ABCF00000010010001101000101111011111化简可得5-13】某汽车驾驶员培训班进行结业考试,有三名评判员,其中A为主评判员为副评判员。在评判时,按照少数服从多数的原则通过,但主评判员认为合格过。用与非门组成的逻辑电路实现此评判规定。解:设合格为1”,通过为1” ;反之为0”。根据题意,列

23、真值表见表 A5.14。表 A5.14ABCF00000010010001101000101111011111化简可得F = AB AC = AB.AC5-14】分析图P5.16所示电路中,当A、B、C、D只有一个改变状态时,是否存在竞争冒险现象?如果存在,都发生在其他变量为何种取值的情况下?ABCD图 5.14解:由图可知表达式为Y = ACD ABD BC CD当 B=0 且 C=D=1 时:Y= A +A当 A=D=1 且 C=0 时:Y=B+ B当 B=1,D=0 或 A=0, B=D=1 时:Y=C+ C当 A=0,C=1 或 A=C=1,B=0 时:Y=D+ D第6章触发器6-1】

24、已知由与非门构成的基本RS触发器的直接置“端和直接置“端的输入波形如图6.1所示,试画出触发器 Q端和Q端的波形。Rd|一Sd|-QQ 图6.1解:基本RS触发器Q端和Q端的波形可按真值表确定,要注意的是,当Rd和Sd同时为 0”时,Q端和Q端都等于1”。Rd和Sd同时撤消,即同时变为1”时,Q端和Q端的状态 不定。见图6.1 (b)所示,图中Q端和Q端的最右侧的虚线表示状态不定 。RdSd不定状态QQ图6.1 (b) 题6-1答案的波形图6-2】触发器电路如图6.2(a)所示,在图(b)中画出电路的输出端波形 ,设触发器初态为解:此题是由或非门构成的RS触发器,工作原理与由与非门构成的基本R

25、S触发器-样,只不过此电路对输入触发信号是高电平有效。参照题6-1的求解方法,即可画出输出端的波形,见图6.2(c)。图 6.2(c)6-3】试画出图6.3所示的电路,在给定输入时钟作用下的输出波形 为 “0”。,设触发器的初态图6.3解:见图6.3(b)所示,此电路可获得双相时钟图 6.3(b)6-4】分析图6.4所示电路,列出真值表,写出特性方程,说明其逻辑功能解:3 .真值表(CP=0时,保持;CP=1时,如下表)DnQnQn+10000101011114 .特性方程Qn+1 = Dn5 .该电路为锁存器(时钟型D触发器)。CP=0时,不接收D的数据;CP=1时,把 数据锁存,但该电路有

26、空翻。6-5】试画出在图6.5所示输入波形的作用下,上升和下降边沿JK触发器的输出波形。 设触发器的初态为“0”。cpJ _I_IK II图6.5解:见图6.5(b)所示。CPJ KQ _I_I_I图 6.5(b)6-6】试画出图P6.6(a)所示电路,在图6.6(b)给定输入下的Q端波形,设触发器初态为CP-.>D(a)c【二ID -'1-I-Q(b)图6.6解:见图6.6(b)所示。CpT_rL_nm.Jvmrud -! Mnj irm !:; I !"!Q I |图 6.6(b)6-7根据特性方程,外加与非门将 D触发器转换为JK触发器,应如何实现?若反过 来将J

27、K触发器转换为D触发器,应如何实现?解:J-K触发器特性方程Qn+=JQn + KQnD触发器特性方程Qn41=DD触发器转换为J-K触发器 D = JQn +KQn =JQn KQ n如图6.7 (a)所示。J-K触发器转换为D触发器 J=D, K=D如图6.7(b)所示。CP(a) (b)图6.76-8】电路如图6.8(a)所示,触发器为维持阻塞型D触发器,各触发器初态均为“ 0”。1 .在图(b)中画出CP作用下的Qo Qi和Z的波形;2.分析Z与CP的关系。(a)CJ 一 一 一 一QoQi_Z(b)图6.8解:1、CP作用下的输出 Qo Qi和Z的波形如下图;2、Z对CP三分频。6-

28、9】电路如图6.9(a)所示,试在图(b)中画出给定输入波形作用下的输出波形,各触发器的初态均为“0”根据输出波形,说明该电路具有什么功能?FFoFFiA 1D Q >C1CP(a) cpIA -F(b) 图6.9 解:输出波形图见图6.9(c)cP-rLn-TLnT-LrLm|31IA:F 图 6.9(c)6-10】电路如图6.10所示,试在图(b)中画出给定输入波形作用下输出端Q0和Qi的波AAQ0Q1 (a)CP 一一 一 一 一一一形,设各触发器的初态均为“0”。(b)图 6.10解:输出波形图见图6.10(c)图 6.10(c)6-11】电路如图6.11所示,试在图(b)中画出

29、给定输入波形作用下输出端Q0和Qi波1' AFF0(a)形,各触发器的初态均为“0”。CP_LT二AI u IQ0_Q1(b)图 6.11解:见图6.11(b)所示。该电路A输入每出现一次下降沿,Q1端就输出一个宽度等于时钟周 期的脉冲。cp_-_Lr_-_rL_LA _L_._IXJJl IQ。门_巾LQ1|; I I图 6.11(b)第7章时序逻辑电路7-1】已知时序逻辑电路如图7.1所示,假设触发器的初始状态均为0。(1 )写出电路的状态方程和输出方程。(2)分别列出X=0和X=1两种情况下的状态转换表,说明其逻辑功能画出X=1时,在CP脉冲作用下的 Qi、Q2和输出Z的波形。图

30、7.1解:1 .电路的状态方程和输出方程Qin1 =XQnQ;QnQ2 1 ; Qin 二 Q;Z =Q102cp2 .分别列出X=0和X=1两种情况下的状态转换表,见题表7.1所示。逻辑功能为 当X=0时,为2位二进制减法计数器;当X=1时,为3进制减法计数器。3 . X=1时,在CP脉冲作用下的 Q1、Q2和输出Z的波形如图7.1(b)所示。X=0X=1Q2Q1Q2Q1000011101001010000题表7.17.1(b)7-2】电路如图7.2所示,假设初始状态 QaQbQc=000。(1)写出驱动方程、列出状态转换表、画出完整的状态转换图(2)试分析该电路构成的是几进制的计数器。解:

31、图7.2Ja1 .写出驱动方程=Ka =1 Jb=Kb=Q;Q:Jc=Q;Q:Kc=Q;2 .写出状态方程Qn 1 =Q:QbQc QanQcnQ;1 =QnQn 1 =QMQ?QanQnQ;3 .列出状态转换表见题表 7.2,状态转换图如图7.2(b)所示。CPQc Qbn Qn0000100120103011410051016000表 7.2状态转换表图 7.2(b)4 .由FFa、FFb和FFc构成的是六进制的计数器 。7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q或Q)填入下表触发方式计数器类型上升沿触发加法计数器由()端引出进位减法计数器由()端引出借位下降沿触发由()端

32、引出进位由()端引出借位解:题表7-3触发方式加法计数器减法计数器上升沿触发由Q端引出进位由Q端引出借位下降沿触发由Q端引出进位由Q端引出借位7-4】电路如图7.4(a)所示,假设初始状态 Q2Q1Qo=000。1.试分析由FF1和FFo构成的是几进制计数器;2.说明整个电路为几进制计数器 。列出状态转换表,画出完整的状态转换图和 CP作用下的波形图(a)图7.4C_TLQ 0Q1 iiirrQ2(b)解:2、整个电路为六进制计数器。状态转换表(略),完整的状态转换图和CP作用下的波形图如下图7-5】某移位寄存器型计数器的状态转换表如表7.5所示。请在图7.5中完成该计数器的逻辑图,可以增加必

33、要的门电路。要求:写出求解步骤、画出完整的状态转换图(Q3为高位)图7.5解:(1)根据状态转换表画次态卡诺图,求出状态方程。1、由ER和F%构成的是三进制加法计数器(过程从略)Qn+13(2)由状态方程写驱动方程Qn+1=QiD3=Q1用;D2=Q3n; Di=Q2n; D0=Qin(3)验证自启动,画完整状态转换图电路可自启动。03(4)电路图如下图7-6在图7.6(a)所示电路中,由D触发器构成的六位移位寄存器输出Q6 Qs Q4 Q3 Q2Qi的初态为010100,触发器FF的初态为0,串行输入端Dsr=0。请在图7.6 (b)中画出A、CP(a)Q及B的波形。(b)图7.6解:波形图

34、如图7.6(b)所示。B -图 7.6(b)(a)7-7】分析图7.7所示电路,说明它们是多少进制计数器?一etQd Qc Qb QaEP 74LS161 RCOCPA CP D C B A CR LD i4piL(b)图7.7解:图(a),状态转换顺序QdQcQbQa=0T 1T2T3T4T 5T 产0,是7进制计数器;图(b), QdQcQbQa=6T7T 8T 9-M0T11T 12T 13T 14T 15T 6,是 10 进制计数 器;7-8】分析图7.8所示电路的工作过程1 .画出对应CP的输出QaQdQcQb的波形和状态转换图(采用二进制码的形式Qa为局位)。2 .按QaQdQcQ

35、b顺序电路给出的是什么编码?3 .按QdQcQbQa顺序电路给出的编码又是什么样的?CP> CPB QA QB QC QD74LS90> CPA S0(2) S0(1)R0(2) R0(1)图7.8解:1状态转换图为2按QaQdQcQb顺序电路给出的是 5421码。3.按QdQcQbQa顺序电路给出的编码如下 0000 0010 0100 0110 1000 0001 0011 0101 0111 1001 00007-10试用2片4位二进制计数器 74LS160采用清零法和置数法分别实现31进制加法计数器。解:答案略。7-9】图7.9为由集成异步计数器 74LS90、74LS93

36、构成的电路,试分别说明它 们是多少进制的计数器。CPB Qa Qb Qc Qd74LS90CPASo(2) So(1) Ro(2) Ro(1)CPCPB QA QB QC QD74LS93CPAR0(2) R0(1)(a)(b)解:图(a),状态转换顺序QdQcQb=0t 1T2T0,是3进制计数器;图(b),状态转换顺序QdQcQb=0-Mt2T 3T0,是4进制计数器;图(c),是37进制计数器。7-11图7.12所示为一个可变进制计数器 。其中74LS138为3线/8线译码器,当Si=1 且S2 =S3 =0时,进行译码操作,即当A2A1A0从000到111变化时,YiY7依次被选中而

37、输出低电平。74LS153为四选一数据选择器。试问当MN为各种不同取值时,可组成几种 不同进制的计数器?简述理由。图 7.11解:4个JK触发器构成二进制加法计数器,当计数到Q4Q3Q2Q1=10000时,74LS138满足使能条件,又Q3Q2Qi的状态进行译码,译码器的输出Y经过4选1数据选择器74LS153 ,在MN的控制下,被选中的 Y信号,以低电平的形式对计数器清零。不同的MN即可改变图7.11所示电路的计数进制,具体见下表。MN进制00八01九10十四11word资料可编辑第8章存储器8-1 填空1. 按构成材料的不同,存储器可分为磁芯和半导体存储器两种。磁芯存储器利用来存储数据;而

38、半导体存储器利用 来存储数据。两者相比,前者一般容量较 ;而后者具有速度 的特点。2. 半导体存储器按功能分有 和 两种。3. ROM主要由 和 两部分组成。按照工作方式的不同进行分类,ROM可分为、和三种。4. 某EPROM有8条数据线,13条地址线,则存储容量为 。5. DRAM 速度 SRAM ,集成度 SRAM。6. DRAM是 RAM ,工作时(需要,不需要)刷新电路;SRAM是RAM ,工作时(需要,不需要)刷新电路。7. FIFO的中文含义是 。解:1 .正负剩磁,器件的开关状态,大,快。2 . ROM , RAM。3 .地址译码器,存储矩阵,固定内容的 ROM、 PROM ,

39、EPROM三种。4 . 213X8。5 .低于,高于。6 .动态,需要;静态,不需要。7 .先进先出数据存储器。B-2】图8.2是16X4位ROM , A3A2A1A0为地址输入,D3D2D1D0为数据输出,试分别写出D3、D2、Di和Do的逻辑表达式图8.2解:Do=AoD1 =£m(3,6,9,12,15)D3=£m(0,5,9,13)8-3】用16X4位ROM做成两个两位二进制数相乘(A1A0X3B0)的运算器,列出真值表, 画出存储矩阵的阵列图解:图8.3B-4】由一个三位二进制加法计数器和一个ROM构成的电路如图8.4(a)所示1 .写出输出Fi、F2和F3的表达

40、式;(a)2 .画出CP作用下Fi、F2和F3的波形(计数器的初态为"0 ")cp 一 口 一 I Ji-llIIIIIIF1111IIIIIIIIF2illIIIIIIIIF3111(b)图8.4解:R =Qi Q0 +Q2 Qi +Q2 Q1Q01.什2=0! Q1Q0+Q2QX+Q2 Q1QF3 =Q1 Q02.8-5】用ROM实现全加器。解:word资料可编辑第9章 可编程逻辑器件及 Verilog语言9-1】简述CPLD与FPGA的结构特点?解:CPLD采用了与或逻辑阵列加上输出逻辑单元的结构形式;而FPGA的电路结构由若独立的可编程逻辑模块组成,用户可以通过编程

41、将这些模块连接成所需要的数字系统CPLD属于粗粒结构,FPGA属于细粒结构。CPLD是基于乘积项的可编程结构而在FPGA中,其基本逻辑单元 LE是由可编程的查找表(LUT, Look-Up Table )构成的,LUT本质上就是一个RAM 。9-2】简述手工设计与 PLD设计的流程?解:答:手工设计:第一步,设计电路,画出逻辑图;第二步,选择逻辑元器件。第三步,进行正确的连线。PLD的设计流程:首先根据设计要求写出相应的逻辑表达式,画出设计草图计算机上利用PLD软件通过原理图输入方式或硬件描述语言(HDL)输入方式输入逻辑设计描述,经计算机仿真验证后,下载到PLD器件中,最后再通过外部实际输入

42、输出对设计进行验证。9-3】用PLD器件实现的电路仿真结果如图9.4所示,请指出电路的功能。Name: Value50口,口g1 Ous 1 5us 2,Ous 2 5us 3 Ousrmll一 龊爪 Um rl U押unn n n IMfflW Lrmmmmimnwmiiw(a)Name:Value:tf-DUL0rt-CLK0Q1100.0ns 200.0ns 300.0ns 400.0ns 500.0ns 600.(Value: a0(b)(c)图9.4Name:A D-CLM4_> Q解:图P9.4 (a)为二选一数据选择器,图P9.4 (b)边沿型D触发器,图P9.4 (c)为

43、电平触发D触发器。9-4 iVerilog语言程序清单如下,写出电路的逻辑功能,并通过QuartusII进行仿真。module count(out,data,load,reset,clk);output7:0 out;input7:0 data;input load,clk,reset;reg7:0 out;always (posedge clk)beginif (!reset) out = 8'h00;else if (load) out = data;else out = out - 1;endendmodule解:Verilog语言程序清单如下,写出电路的逻辑功能,并通过Quar

44、tusII进行仿真。module count(out,data,load,reset,clk);output7:0 out;input7:0 data;input load,clk,reset;reg7:0 out;always (posedge clk)beginif (!reset) out = 8'h00;else if (load) out = data;else out = out - 1;endendmodule9-5 iVerilog语言程序清单如下,写出电路的逻辑功能表,并通过QuartusII进行仿真。module yima(A,EN,Y);output 7:0 Y;

45、input 2:0 A;input EN;reg7:0 Y;wire 3:0 temp=A,EN;alwayscase (temp)4'b0001 : Y=8'b00000001;4'b1001 : Y=8'b00000010;4'b0101 : Y=8'b00000100;4'b1101 : Y=8'b00001000;4'b0011 : Y=8'b00010000;4'b1011 : Y=8'b00100000;4'b0111 : Y=8'b01000000;4'b111

46、1 : Y=8'b10000000;default : Y=8'b11111111;endcaseendmodule解:P9.5(b)。3输入8输出译码器。仿真波形图见P9.5(a),仿真电路图见(a)仿真波形图WideOrO-4A1AIOJA2DATAADATAEW M PU U 1* 1 r JDATACATADLOG C_CIELL_COME (JaFOTiWideOMMDATMDATAE lc u ami it_ _ _'.vrsiUU HI vU'U 1>> 丫回OATACDATAOLOG IC-CIELL_COME 型砌WideOr2MD

47、ATA*DATABGQIIDU U nDATW:DATA 口M产 TPJLOCIC_CELL_CO W B (BOFiWideOr34ATAADATAB.M|/l J 1COMBO LITo* >n4lATACATADLDGC_CELL_COUB(FOSCDWideOr4-4ATAADATABUETLU M nu U 1OATACDATAD0LOCIC_CELL_COII B (DOFWide0r5MDATMATAB riA U AA i ITWM VU U IDATACDATADtkJLOG C_CELL_COII B (FQDO)WideOr64DATAADATAE ca u nni

48、 itUU H vU'U 1"Mr 川DATiRCDATADLOG C_CELL_COH5 (HJFWidsOr7-4OATAADATA6COMBO UTDATACDATA 口LDCC_CELL_COM&(b)仿真电路图图9.59-6】Verilog语言程序清单如下,写出电路的逻辑功能表,并通过QuartusII进行仿真。module bianma(Y,A);output 2:0 A;input 7:0 Y;reg 2:0 A;wire 7:0 temp=Y;alwayscase (temp)8'b00000001: A=3'b000;8'b00000010: A=3'b100;8'b00000100: A=

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 阿尔兹海默症常见症状及护理方法探讨

- 赠与请求归还协议书

- 联营股东协议书范本

- 断桥铝门安装合同范本

- 代理人签字合同范本

- 个人项目参股协议书

- 监理合同不收钱写协议

- 资金委托代理协议书

- 分工合同协议书样本

- 电池意向供货协议书

- 2025-2030航空复合材料损伤监测技术与维护成本控制报告

- 2025年国家普通话水平测试题及答案

- 《医疗机构工作人员廉洁从业九项准则实施细则(试行)》解读学习

- 智能终端与用户行为分析-洞察与解读

- 绳降基础知识培训课件

- 煤矿环保知识培训记录课件

- 中山市介绍模板

- 哮喘讲座课件

- 酒店投资(合作)协议(书)范本7篇

- SimBank银行模拟教学平台实习指导书

- 2025年安徽省交通控股集团六安北高速公路管理中心见习人员招聘15名备考考试题库附答案解析

评论

0/150

提交评论