下载本文档

版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、?数字逻辑?教学大纲、根本信息课程代吗:1252612课程性质:专业限选课课程名称:数字避辑英文名称:DigitalLogic学时/学分:32/2开课时间:大二下适用对象:计算机科学与技术、网络工程、软件工程、信息平安等专业先修课程:大学物理、高级语言程序设计大纲执笔人:傅均大纲审核人:邢建国修订时间:2021-12当前版本:2021二、课程描述本课程为专业限定选修课,主要面向计算机科学与技术、网络工程、软件工程、信息安全等专业本科低年级学生.主要目的是使学生掌握数字逻辑电路的根本概念和分析、设计方法,作为专业前导课程,为以后的专业核心课程?计算机组成结构?及其他硬件类课程?微机原理和接口技术

2、?、?嵌入式系统开发技术?等的学习打下良好的根底.本课程是为缺少电路原理、模拟电子技术等先修课程的计算机与信息学科偏软类专业开设,其要求和难度略低于电子信息学科偏硬类专业,通过该课程的学习使学生掌握数字逻辑电路的应用和开展及逻辑代数等根本知识唾点掌握组合逻辑电路和同步时序逻辑电路的分析和设计等根本方法,使学生具有一定的数字逻辑电路设计水平.另外,使学生了解可编程逻辑器件和现代数字系统设计方法,初步掌握运用EDA工具及硬件描述语言进行简单数字逻辑设计,紧跟市场和技术前沿.三、教学目标通过本课程的理论教学和相关实验练习,使学生具备如下水平:1、掌握根本的逻辑代数知识,能够运用物理知识理解二极管、三

3、极管、集成逻辑门和可编程逻辑器件的根本原理.2、能够运用逻辑代数方法表达、求解和优化实际数字电路问题,3、能够分析小规模、中规模组合逻辑电路和时序逻辑电路,掌握各种逻辑门、根本触发器、中规模集成器件的功能及根本应用.4、能够利用逻辑门、根本触发器、中规模集成器件和可编程逻辑器件设计一定功能的组合逻辑电路和时序逻辑电路,并进行优化.5、能够应用专业EDA软件设计一定功能的数字系统,并能进行仿真和脸证.四、课程目标对毕业要求的支撑毕业要求指标点课程目标6、具备扎实的数学、自然科学根底及根本的经管类知识,以及较好外的英语应用水平6.1具有扎实的数学和自然科学根底知识教学目标17、掌握专业知识与技能,

4、具有理解和表达复杂工程问题的水平7.1系统掌握本专业所需的高级语言、数据结构、操作系统、计算机组成原理、数据库等专业根底理论知识教学目标27.2掌握信息检索和数据分析等专业技能及其相关工具的使用教学目标59、具备复杂计算机应用系统的分析、设计、开发和维护水平9.1具有较强的分析问题水平教学目标39.2能够综合运用所学知识,应用相关工具进行计算机软硬件工程问题的系统设计、开发和维护教学目标4五、教学容第1章绪论支撑课程目标1重点容:数制和编码的概念,各种不同数制间的转换方法,二进制的运算及原、反、补码数的表示及转换,二-十进制代码BCD代码.难点容:建立模拟信号和数字信号的概念,二进制的运算及原

5、、反、补码数的表示.教学容:掌握数制及其转换,编码的概念,了解常用码的一些应用,热悉数字编码的转换°1.1数字电路逻辑设计概述1. 2数制及其转换1.3 二-十进制代码BCD代码1.4 算术运算与逻辑运算第2章逻辑函数及其简化支撑谭程目标1、2重点容:逻辑代数的各种表达形式,逻辑代数的三个规那么和常用公式,逻辑代数的化简方法,卡诺图法.难点容:简单逻辑命题建立逻辑函数的方法.教学要求:掌握逻辑代数根本定理'根本规那么和常用公式,掌握用代数法和卡诺图法简化逻辑函数的方法,掌握由简单逻辑命题建立逻辑函数的方法.2.1 逻辑代数2. 2逻辑函数的简化第3章集成逻辑门支撑课程目标1重

6、点容:二极管与三极管的开关特性.TTL集成逻辑门的主要外部特性.难点容:二极管和三极管的开关特性,TTL集成逻辑门的工作原理.教学要求:了解二极管和三极管的开关特性,掌握通用数字集成电路的分类,了解TTL门的工作原理、主要外特性.3. 1晶体管的开关特性3.2TTL集成逻辑门第4章组合逻辑电路支撑课程目标3、4重点容:组合逻辑电路概念、组合逻辑电路的分析与设计方法,全加器、编码器、译码器、数值比拟器、数据选择器等常用组合逻辑功能器件,采用常用的小规模、中规模集成器件进行组合逻辑电路设计.难点容:组合逻辑电路的冒险现象,产生冒险的原因,判断与防止冒险的方法.教学要求:掌握全加器、编码器、译码器、

7、数值比拟器、数据选择器等常见中规模组合逻辑器件的逻辑功能与应用,掌握采用小规模和中规模集成器件的组合逻辑电路设计方法,理解组合逻辑电路的冒险现象以及如何防止冒险.4. 1组合逻辑电路分析4. 2组合逻辑电路设计4.3组合逻辑电路的冒险现象第5章集成触发器支撑课程目标3、4重点容:根本触发器、钟控触发器、主从触发器、边沿触发器的电路结构与功能特点,触发器逻辑功能的描述方法,触发器类型转换.难点容:钟控T触发器的空翻与主从J-K触发器主触发器的一次翻转现象.教学要求:理解集成触发器电路组成和工作原理,掌握集成触发器功能的描述方法和脉冲工作特性,了解不同类型集成触发器的转换方法.重点掌握集成触发器的

8、应用.5. 1根本触发器5. 2钟控触发器5.3 主从触发器5.4 边沿触发器第6章时序逻辑电路支撑课程目标3、4重点容:时序电路的分析方法:驱动方程、输入方程、状态转移方程、状态转移表、状态转移图和时序图,常用时序电路:存放器、移位存放器、同步计数器等.时序电路的设计方法:设计原那么和一般步骤,采用小规模集成器件设计同步计数器,采用中规模集成器件设计任意模值计数分频器.难点容:小规模同步时序逻辑电路分析方法,采用中规模集成器件实现任意模值计数分频器的方法.教学要求:掌握时序逻辑电路的根本概念,掌握小规模同步时序逻辑电路分析和设计方法,掌握采用中规模集成器件实现任意模值计数分频器的方法.6.

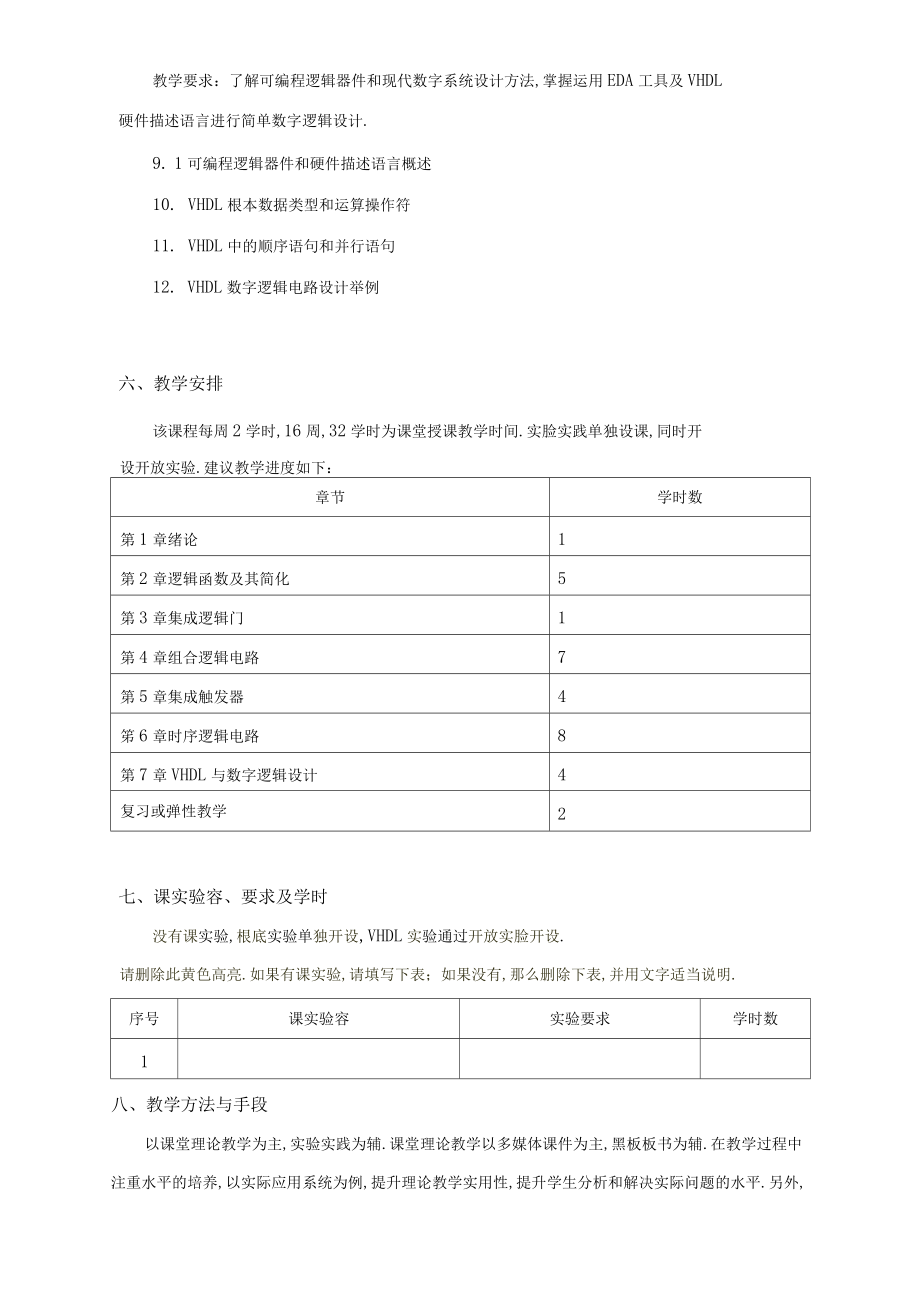

9、1时序逻辑电路概述7. 2时序逻辑电路分析8. 3时序逻辑电路设计第7章VHDL与数字逻辑设计支撑课程目标3、4、5重点容:VHDL语言的根本结构、数据类型、语句和设计方法.难点容:可编程逻辑器件,现代数字系统设计方法,VHDL中的并行语句.教学要求:了解可编程逻辑器件和现代数字系统设计方法,掌握运用EDA工具及VHDL硬件描述语言进行简单数字逻辑设计.9. 1可编程逻辑器件和硬件描述语言概述10. VHDL根本数据类型和运算操作符11. VHDL中的顺序语句和并行语句12. VHDL数字逻辑电路设计举例六、教学安排该课程每周2学时,16周,32学时为课堂授课教学时间.实脸实践单独设课,同时开

10、设开放实验.建议教学进度如下:章节学时数第1章绪论1第2章逻辑函数及其简化5第3章集成逻辑门1第4章组合逻辑电路7第5章集成触发器4笫6章时序逻辑电路8第7章VHDL与数字逻辑设计4复习或弹性教学2七、课实验容、要求及学时没有课实验,根底实验单独开设,VHDL实验通过开放实脸开设.请删除此黄色高亮.如果有课实验,请填写下表;如果没有,那么删除下表,并用文字适当说明.序号课实验容实验要求学时数1八、教学方法与手段以课堂理论教学为主,实验实践为辅.课堂理论教学以多媒体课件为主,黑板板书为辅.在教学过程中注重水平的培养,以实际应用系统为例,提升理论教学实用性,提升学生分析和解决实际问题的水平.另外,本课程开设Blackboard电子教学平台,学生可以进行自主学习、提交作业、讨论问题.鼓励学生参加开放实验*在平时VHDL实脸作业根底上进一步提升EDA设计水平.九、考核方式及成绩评定考核方式:期末测试闭卷,平时作业、出勤、课堂情况,VHDL实验作业.成绩评定标准:总成绩百分制=平时成绩x30%+VHDL实验xlO%+期末测试成绩x60%.十、教材及主要参考书指定教材:1 '王毓银主编,数字电路逻辑设计第二版,高等教育,2005.122 &

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 数字化转型背景下本科教学督导体系的创新

- 公共管理研究生数字素养提升策略的优化探讨

- 鹿寨中学模拟考试题目及答案

- 2025年榆树事业单位真题

- 湖南农业发展投资集团有限责任公司招聘笔试真题2024

- 多金属协同冶炼-洞察与解读

- 铝土矿无人化开采-洞察与解读

- 消防救援员面试题及答案

- 许慎中学考试题目及答案

- 数字经济人才需求预测-洞察与解读

- 第6课 推动形成全面对外开放新格局高一思想政治《中国特色社会主义》同(高教版2023基础模块)

- 社会调查研究抽样课件

- 矩阵论同步学习辅导 张凯院 西北工业大学出版社

- 英语英语句子成分和基本结构

- GB/T 24218.1-2009纺织品非织造布试验方法第1部分:单位面积质量的测定

- GB/T 10357.1-2013家具力学性能试验第1部分:桌类强度和耐久性

- GB 16541-1996竖井罐笼提升信号系统安全技术要求

- GB 10068-2000轴中心高为56mm及以上电机的机械振动振动的测量、评定及限值

- 电焊工模拟试题(含答案)

- 全国优质课一等奖初中数学《有理数的乘方》精品课件

- 施工现场临时用电安全检查验收表

评论

0/150

提交评论