版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

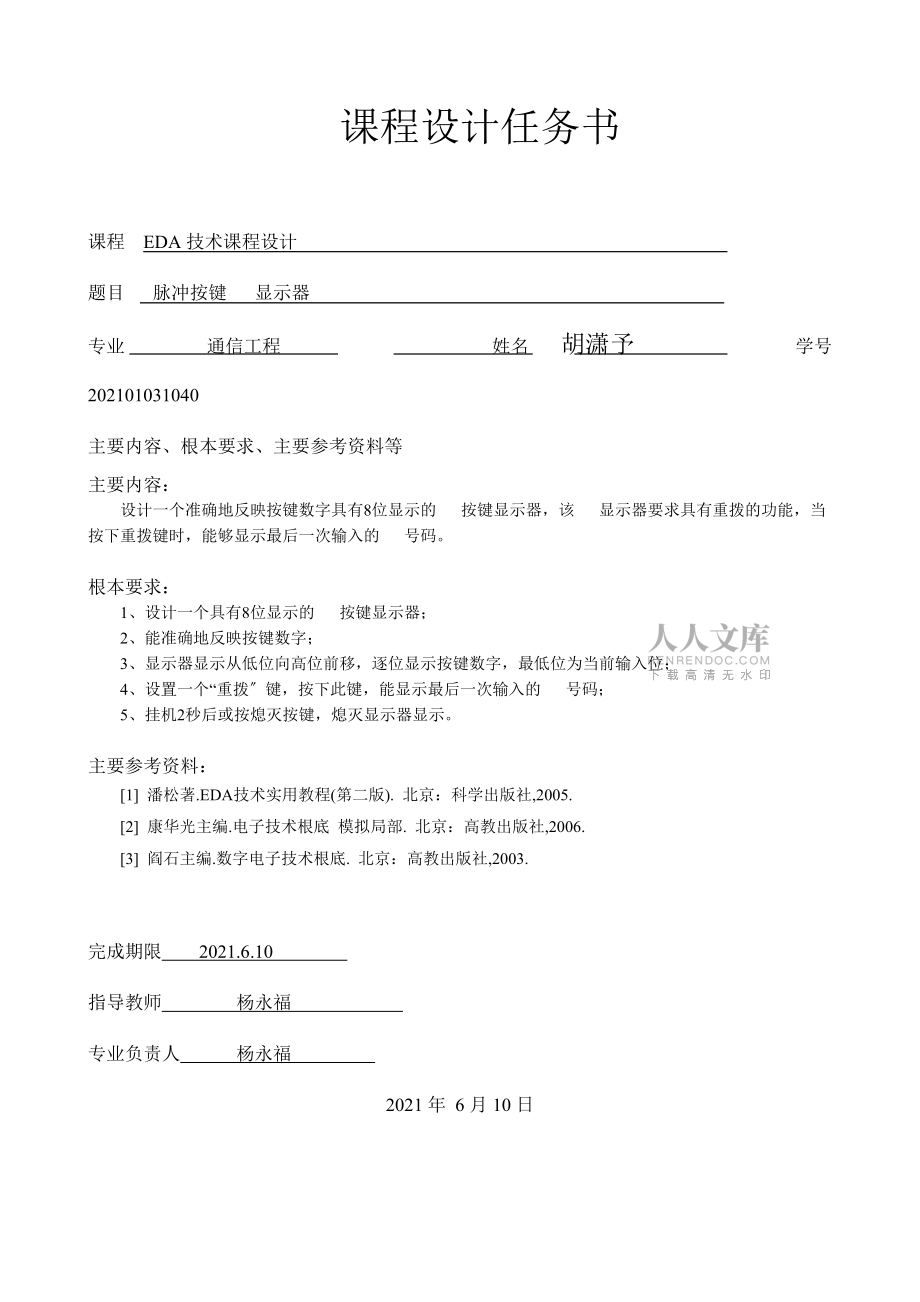

1、 课 程 设 计课 程 EDA技术课程设计 题 目 脉冲按键 显示器 院 系 工学院 专业班级 13通信 学生姓名 胡潇予 学生学号 202101031040 指导教师 杨永福 2021年 6 月10日 课程设计任务书课程 EDA技术课程设计题目 脉冲按键 显示器专业 通信工程 姓名 胡潇予 学号 202101031040主要内容、根本要求、主要参考资料等主要内容:设计一个准确地反映按键数字具有8位显示的 按键显示器,该 显示器要求具有重拨的功能,当按下重拨键时,能够显示最后一次输入的 号码。根本要求:1、设计一个具有8位显示的 按键显示器;2、能准确地反映按键数字;3、显示器显示从低位向高位

2、前移,逐位显示按键数字,最低位为当前输入位;4、设置一个“重拨键,按下此键,能显示最后一次输入的 号码;5、挂机2秒后或按熄灭按键,熄灭显示器显示。主要参考资料:1 潘松著.EDA技术实用教程(第二版). 北京:科学出版社,2005.2 康华光主编.电子技术根底 模拟局部. 北京:高教出版社,2006.3 阎石主编.数字电子技术根底. 北京:高教出版社,2003.完成期限 2021.6.10 指导教师 杨永福 专业负责人 杨永福 2021年 6月10日 一、总体设计思想1.根本原理此题目是用VHDL语言实现一个能准确地反映按键数字、具有8位显示 的 按键显示器。摘机时开始工作,显示器显示从低位

3、向高位前移,逐位显示按键数字,最低位为当前输入位;设置一个“重拨键,按下此键能显示最后一次输入的 号码;挂机2秒后或按熄灭键,熄灭显示器显示。脉冲按键 显示器由五个模块组成:按键电路、译码器、移位存放、锁存器和数码管显示电路,其中移位存放、锁存器和数码管译码显示电路为系统的主要组成局部。1按键电路模块。提供“0到“9数字按键的输入,同时设置有拨号 键,去除键,挂机键和重拨键。2译码电路模块。译码器有两个功能。第一,把输入的一位键值转换成 四位 BCD 码;第二,把四位二进制码译成相应的数码管输出显示码。3移位存放器、锁存模块。移位存放器分为三个局部。当按下拨号键时, 数字按键值依次由数码管的低

4、位向高位移动,同时送入锁存器中;当按下删除 键时,键值由高位向低位移除,高位数码管熄灭;当按下重拨键时,锁存器中 存储的键值输入到移位存放器中,并通过数码管显示出来。4数码管显示模块。数码管显示用于将设置好的每个按键的键值在数码 管上显示出来。由于实验过程中需要使用8个数码管,因此数码管显示模块必须加上数码管片选及移位得程序,从而实现数据输入以后从低位向高位移动、显示。2.设计框图数字键入控制电路1译码显示器移位存放器脉冲产生电路控制电路2计时电路译码显示电路图1 整体设计框图二、设计步骤和调试过程1、总体设计电路图2总体设计电路2、模块设计和相应模块程序(1) 顶层文件程序LIBRARY I

5、EEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY UPKEY ISPORT(DIN1:IN STD_LOGIC_VECTOR(9DOWNTO 0); CLK1,CLEAR,DIAL,RE_DIAL:IN STD_LOGIC;KEYOUT:OUT STD_LOGIC; SEG71:OUT STD_LOGIC_VECTOR(6 DOWNTO 0); SEG8:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); END ENTITY; ARCHITECTURE ONE OF UPKEY

6、IS COMPONENT SHOW IS PORT(DIN:IN STD_LOGIC_VECTOR(9 DOWNTO 0);CLK,CLEAR,DIAL,RE_DIAL:IN STD_LOGIC; KEYOUT:OUT STD_LOGIC; SET:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); SEG8:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);END COMPONENT;COMPONENT TRA ISPORT(BCD1:IN STD_LOGIC_VECTOR(3 DOWNTO 0);SEG7:OUT STD_LOGIC_VECTOR(6 DOW

7、NTO 0); END COMPONENT; SIGNAL SET_1:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGIN U1:SHOW PORT MAP( DIN1,CLK1,CLEAR,DIAL,RE_DIAL,KEYOUT,SET_1,SEG8); U2:TRA PORT MAP(SET_1,SEG71); END ARCHITECTURE ONE; (2)译码器译码局部的设计图3 BCD译码电路图BCD译码子程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTI

8、TY TRA IS PORT( BCD1:IN STD_LOGIC_VECTOR(3 DOWNTO 0); SEG7:OUT STD_LOGIC_VECTOR(6 DOWNTO 0); END ENTITY; ARCHITECTURE ONE OF TRA IS BEGIN PROCESS(BCD1)IS BEGIN CASE BCD1 IS WHEN "0000"=>SEG7<="0111111"WHEN "0001"=>SEG7<="0000110" WHEN "0010&qu

9、ot;=>SEG7<="1011011" WHEN "0011"=>SEG7<="1001111"WHEN "0100"=>SEG7<="1100110" WHEN "0101"=>SEG7<="1101101" WHEN "0110"=>SEG7<="1111101" WHEN "0111"=>SEG7<="000

10、0111" WHEN "1000"=>SEG7<="1111111" WHEN "1001"=>SEG7<="1101111" WHEN OTHERS=>SEG7<="0000000" END CASE;END PROCESS; END ARCHITECTURE;(3)键值显示局部设计图4按键显示控制电路图按键显示控制子程序:LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_U

11、NSIGNED.ALL; ENTITY SHOW IS PORT(DIN:IN STD_LOGIC_VECTOR(9 DOWNTO 0);CLK,CLEAR,DIAL,RE_DIAL:IN STD_LOGIC; KEYOUT:OUT STD_LOGIC; SET:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); SEG8:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); END ENTITY; ARCHITECTURE ONE OF SHOW IS SUBTYPE TEN IS STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL BCD

12、 :TEN; TYPE NUMBER1 IS ARRAY(7 DOWNTO 0) OF STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL NUMBER : NUMBER1; SIGNAL KEY,KEY1,CLK1,DIAL1,RE_DIAL1:STD_LOGIC; SIGNAL COUNT:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL COUNT1:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL COUNT2:STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL DIN1: STD_LOGIC_

13、VECTOR(9 DOWNTO 0); SIGNAL LOCK: STD_LOGIC_VECTOR(31 DOWNTO 0); BEGINPROCESS(CLK)IS BEGIN IF RISING_EDGE(CLK) THEN COUNT1<=COUNT1+1;END IF; END PROCESS; CLK1<='0' WHEN COUNT1<"1100" ELSE '1' PROCESS(CLK1)IS BEGIN IF RISING_EDGE(CLK1) THEN DIN1(9 DOWNTO 0)<=DIN(9

14、 DOWNTO 0); DIAL1<=DIAL; RE_DIAL1<=RE_DIAL; END IF; END PROCESS; KEY<=(DIN1(0) OR DIN1(1) OR DIN1(2) OR DIN1(3) OR DIN1(4) OR DIN1(5) OR DIN(6) OR DIN1(7) OR DIN1(8) OR DIN1(9); PROCESS(CLK1)IS BEGIN IF FALLING_EDGE(CLK1) THEN IF COUNT2="100" THEN IF CLEAR='0'AND RE_DIAL=&

15、#39;0' THEN KEY1<=KEY; ELSIF CLEAR ='1' AND RE_DIAL='0' THEN KEY1<=CLK; ELSE KEY1<=RE_DIAL1;END IF; COUNT2<="000" ELSE COUNT2<=COUNT2+1; END IF; END IF;END PROCESS;PROCESS(DIN1)IS BEGIN IF DIN1(6)='1' THEN BCD<="0110" ELSIF DIN1(1)=&#

16、39;1' THEN BCD<="0001" ELSIF DIN1(2)='1' THEN BCD<="0010"ELSIF DIN1(3)='1' THEN BCD<="0011" ELSIF DIN1(4)='1' THEN BCD<="0100" ELSIF DIN1(5)='1' THEN BCD<="0101" ELSIF DIN1(0)='1' THEN BCD<

17、;="0000" ELSIF DIN1(7)='1' THEN BCD<="0111" ELSIF DIN1(8)='1' THEN BCD<="1000" ELSIF DIN1(9)='1' THEN BCD<="1001" ELSE BCD<="0000" END IF;END PROCESS;KEYOUT<=KEY1; PROCESS(KEY1)IS BEGIN IF RISING_EDGE(KEY1) THEN

18、 IF CLEAR='0' AND RE_DIAL1='0' THEN NUMBER(7)<=NUMBER(6); NUMBER(6)<=NUMBER(5); NUMBER(5)<=NUMBER(4); NUMBER(4)<=NUMBER(3); NUMBER(3)<=NUMBER(2); NUMBER(2)<=NUMBER(1); NUMBER(1)<=NUMBER(0); NUMBER(0)<=BCD; ELSIF CLEAR='1' AND RE_DIAL1='0' THEN

19、NUMBER(0)<=NUMBER(1); NUMBER(1)<=NUMBER(2);NUMBER(2)<=NUMBER(3); NUMBER(3)<=NUMBER(4);NUMBER(4)<=NUMBER(5); NUMBER(5)<=NUMBER(6); NUMBER(6)<= NUMBER(7); NUMBER(7)<="1111" ELSE NUMBER(7)<= LOCK(31 DOWNTO 28); NUMBER(6)<= LOCK(27 DOWNTO 24); NUMBER(5)<= LOCK(

20、23 DOWNTO 20); NUMBER(4)<= LOCK(19 DOWNTO 16); NUMBER(3)<= LOCK(15 DOWNTO 12); NUMBER(2)<= LOCK(11 DOWNTO 8); NUMBER(1)<= LOCK(7 DOWNTO 4); NUMBER(0)<= LOCK(3 DOWNTO 0); END IF; END IF; END PROCESS; PROCESS(CLK)IS BEGIN IF RISING_EDGE(CLK) THEN COUNT<=COUNT+1;END IF;END PROCESS; PR

21、OCESS(COUNT)IS BEGIN CASE COUNT IS WHEN "0001"=>SET<=NUMBER(7);SEG8<="00000001" WHEN "0011"=>SET<=NUMBER(6);SEG8<="00000010" WHEN "0101"=>SET<=NUMBER(5);SEG8<="00000100" WHEN "0111"=>SET<=NUMBER(4)

22、;SEG8<="00001000" WHEN "1001"=>SET<=NUMBER(3);SEG8<="00010000" WHEN "1011"=>SET<=NUMBER(2);SEG8<="00100000" WHEN "1101"=>SET<=NUMBER(1);SEG8<="01000000" WHEN "1111"=>SET<=NUMBER(4);SEG

23、8<="10000000" WHEN OTHERS=>NULL; END CASE; END PROCESS; PROCESS(DIAL1)IS BEGIN IF RISING_EDGE(DIAL1) THEN LOCK(31 DOWNTO 28)<=NUMBER(7); LOCK(27 DOWNTO 24)<=NUMBER(6);LOCK(23 DOWNTO 20)<=NUMBER(5); LOCK(19 DOWNTO 16)<=NUMBER(4); LOCK(15 DOWNTO 12)<=NUMBER(3); LOCK(11 DOWNTO 8)<=NUMBER(2); LOCK(7 DOWNTO 4)<=NUMBER(1); LOCK(3 DOWNTO 0)<=NUMBER(0); END IF; END PROCESS;END ARCHITECTURE;4、实验调试结果为验证所设计的程序是否正确,将程序下载进行硬件测试。在Quar

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 福利院采购合同范本

- 碧桂园的购房协议书

- 砂石融资承揽协议书

- 电厂签订安全协议书

- 脑卒中后康复训练计划

- 悬吊训练康复技术

- 2026年高端私人影院建设公司销售团队管理制度

- 2025-2026学年广东省汕头市潮阳区某校高一上学期第一次月考试地理试卷(解析版)

- 结肠癌早期症状解析及护理策略

- 工作业绩展示

- 投标文件某光伏电站运维投标文件技术部分

- 刑事模拟法庭培训课件模板

- 2024年中国融通文化教育集团有限公司招聘笔试参考题库含答案解析

- DB34-T 1928-2013 水利水电工程水泥土截渗墙试验测试规程

- 如何培养孩子的良好阅读习惯

- 《化工生产技术》课程标准

- 店长年终总结PPT模板含完整内容12

- 中广核面试开放性问题

- 走进舞蹈艺术-首都师范大学中国大学mooc课后章节答案期末考试题库2023年

- 肿瘤科专业组药物临床试验管理制度及操作规程GCP

- 七年级数学竞赛模拟试题北师大版

评论

0/150

提交评论