版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、专题二:数字钟及校园打铃系统设计一、教学内容:数字钟设计二、教学目的及要求: 1、掌握VHDL语言的基本结构及编程思想。 2、掌握VHDL语言的软件仿真方法。 3、掌握VHDL语言的下载及硬件仿真方法。 4、提高综合应用能力。 三、授课课时:6课时四、教学重点、难点:数字钟VHDL语言设计 数字钟及校园打铃系统设计设计目标: 1、基本的数字钟计时功能、校时功能; 2、定时闹钟功能; 可以任意设定闹钟时间,闹铃时间为1分钟。 3、校园打铃功能; (1)正常教学打铃:分夏季作息时间和春季作息时间打铃,响铃时间20秒。两季作息时间通过开关切换。 (2)考试时间打铃,响铃时间20秒。 (3)正常教学打

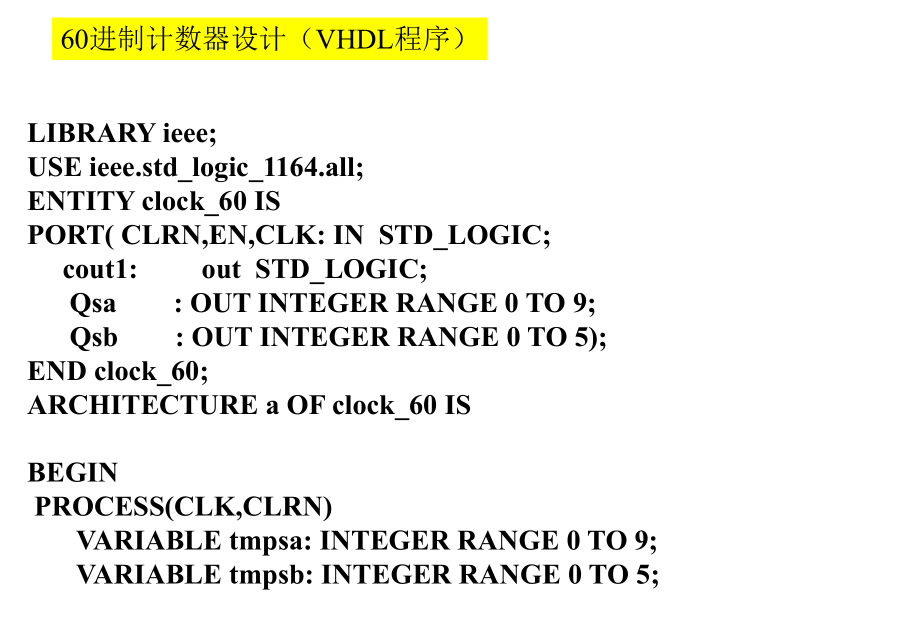

2、铃和考试打铃通过开关切换。一、基本的数字钟计时功能、校时功能电路设计一、基本的数字钟计时功能、校时功能电路设计1、基本计时功能电路设计60进制计数器元件外部引脚功能图元件外部引脚功能图说明:说明:1、EN1时,正常计数,时,正常计数,0时,停止计数。时,停止计数。 2、CLRN0时,复位清零,时,复位清零,1时,正常计数。时,正常计数。 3、CLK时钟信号,上升沿触发。时钟信号,上升沿触发。 4、QSA:60进制个位输出;进制个位输出; QSB:60进制十位输出。进制十位输出。LIBRARY ieee; USE ieee.std_logic_1164.all;ENTITY clock_60 I

3、SPORT( CLRN,EN,CLK: IN STD_LOGIC; cout1: out STD_LOGIC; Qsa : OUT INTEGER RANGE 0 TO 9; Qsb : OUT INTEGER RANGE 0 TO 5);END clock_60;ARCHITECTURE a OF clock_60 IS BEGIN PROCESS(CLK,CLRN) VARIABLE tmpsa: INTEGER RANGE 0 TO 9; VARIABLE tmpsb: INTEGER RANGE 0 TO 5; 60进制计数器设计(VHDL程序)BEGIN IF CLRN=0 THEN

4、 tmpsb := 0; tmpsa := 0; ELSIF CLKevent AND CLK=1 THEN IF EN=1 THEN IF tmpsb=5 AND tmpsa=9 THEN tmpSa:=0; tmpSb:=0 ;COUT1=1; ELSIF tmpSa=9 THEN tmpSa:=0; tmpSb:=tmpSb+1; ELSE tmpSa:=tmpSa+1; END IF; END IF; END IF ; QSA=tmpsa;QSB=tmpsb; END PROCESS ;END a;24进制计数器设计元件外部引脚功能图:进制计数器设计元件外部引脚功能图:说明:说明:1、

5、EN1时,正常计数,时,正常计数,0时,停止计数。时,停止计数。 2、CLRN0时,复位清零,时,复位清零,1时,正常计数。时,正常计数。 3、CLK时钟信号,上升沿触发。时钟信号,上升沿触发。 4、QHA:24进制个位输出;进制个位输出;QHB:24进制十位输出。进制十位输出。LIBRARY ieee; USE ieee.std_logic_1164.all;ENTITY clock_24 ISPORT( CLRN,EN,CLK: IN STD_LOGIC; cout: out STD_LOGIC; Qha : OUT INTEGER RANGE 0 TO 9; Qhb : OUT INTE

6、GER RANGE 0 TO 2);END clock_24;ARCHITECTURE a OF clock_24 IS BEGIN PROCESS(CLK,CLRN) VARIABLE tmpha: INTEGER RANGE 0 TO 9; VARIABLE tmphb: INTEGER RANGE 0 TO 2; 24进制计数器设计BEGIN IF CLRN=0 THEN tmphb := 0; tmpha := 0; ELSIF CLKevent AND CLK=1 THEN IF EN=1 THEN IF tmphb=2 AND tmpha=3 THEN tmpha:=0; tmph

7、b:=0 ;COUT=1; ELSIF tmpha=9 THEN tmpha:=0; tmphb:=tmphb+1; ELSE tmpha:=tmpha+1; END IF; END IF; END IF ; QHA=tmpha;QHB=tmphb; END PROCESS ;END a;数字钟实体数字钟实体数字钟实体数字钟实体 LIBRARY ieee; USE ieee.std_logic_1164.all;ENTITY clock_v ISPORT( EN,CLK,CLRN : IN STD_LOGIC; QSa,QMa,QHa : OUT INTEGER RANGE 0 TO 9; Q

8、Sb,QMb : OUT INTEGER RANGE 0 TO 5; QHb : OUT INTEGER RANGE 0 TO 2 ; cout: out std_logic );END clock_v;ARCHITECTURE a OF clock_v IS signal cout1,cout2,COUT3:STD_LOGIC; BEGINu60s: PROCESS(CLK,CLRN) VARIABLE tmpsa: INTEGER RANGE 0 TO 9; VARIABLE tmpsb: INTEGER RANGE 0 TO 5; BEGIN IF CLRN=0 THEN tmpsb :

9、= 0; tmpsa := 0; ELSIF CLKevent AND CLK=1 THEN IF EN=1 THEN IF tmpsb=5 AND tmpsa=9 THEN tmpSa:=0; tmpSb:=0 ;COUT1=1; ELSIF tmpSa=9 THEN tmpSa:=0; tmpSb:=tmpSb+1; COUT1=0; ELSE tmpSa:=tmpSa+1;COUT1=0; END IF; END IF; END IF ; QSA=tmpsa;QSB=tmpsb; END PROCESS u60s; 数字钟VHDL程序的结构体部分接下页u60M: PROCESS(cout

10、1,CLRN) VARIABLE tmpMa: INTEGER RANGE 0 TO 9; VARIABLE tmpMb: INTEGER RANGE 0 TO 5; BEGIN IF CLRN=0 THEN tmpMb := 0; tmpMa := 0; ELSIF COUT1event AND COUT1=1 THEN IF EN=1 THEN IF tmpMb=5 AND tmpMa=9 THEN tmpMa:=0; tmpMb:=0 ;COUT2=1; ELSIF tmpMa=9 THEN tmpMa:=0; tmpMb:=tmpMb+1; COUT2=0; ELSE tmpMa:=t

11、mpMa+1;COUT2=0; END IF; END IF; END IF ; QMA=tmpMa;QMB=tmpMb; END PROCESS u60M;数字钟分计数器接下页 u24H: PROCESS(COUT2,CLRN) VARIABLE tmpHa: INTEGER RANGE 0 TO 9; VARIABLE tmpHb: INTEGER RANGE 0 TO 2; BEGIN IF CLRN=0 THEN tmpHb := 0; tmpHa := 0; ELSIF COUT2event AND COUT2=1 THEN IF EN=1 THEN IF tmpHb=2 AND t

12、mpHa=3 THEN tmpHa:=0; tmpHb:=0 ;COUT3=1; ELSIF tmpHa=9 THEN tmpHa:=0; tmpHb:=tmpHb+1; COUT3=0; ELSE tmpHa:=tmpHa+1;COUT3=0; END IF; END IF; END IF ; QHA=tmpHa;QHB=tmpHb;COUT=COUT3; END PROCESS u24H;END a;数字钟时计数器结构图结构图NO.7:此电路适合于设计时钟、定时器、秒表等。因为可利用键8和键5分别控制时钟的清零和设置时间的使能;利用键7、5和1进行时、分、秒的设置。D16D15D14D13

13、D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图SPEAKER扬声器FPGA/CPLD目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器原理图设计方法带校时电路的数字钟电路设计带校时电路的数字钟电路设计状态机状态图2选选1多路选

14、择器多路选择器vhdl程序程序ENTITY mux21a IS PORT( a, b : IN BIT ; k : IN BIT; c : OUT BIT ) ;END ENTITY mux21a ;ARCHITECTURE one OF mux21a IS BEGIN c = a WHEN k = 1 ELSE b ;END ARCHITECTURE one ;状态机程序LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL;ENTITY zhuantaiji ISPORT ( CLK 0,reset: IN STD_LOGIC; y : OUT STD_LOGI

15、C_VECTOR(2 DOWNTO 0);END zhuantaiji;ARCHITECTURE behav OF zhuantaiji IS TYPE states IS (st0, st1, st2, st3,st4); SIGNAL stx : states ; BEGIN COMREG : PROCESS(CLK,RESET) BEGIN -决定转换状态的进程决定转换状态的进程 IF RESET =1 THEN STX STX STX STX STX STX y y y y Q=“111 ; END CASE ; END PROCESS COM1 ; END behav; 二、定时闹钟

16、功能电路设计二、定时闹钟功能电路设计定时器控制电路定时器控制电路复位复位定时时间存储电路定时时间存储电路调时或调分调时或调分选择开关选择开关“”键键分分输输出出时时输输出出基本数字钟电路基本数字钟电路秒脉冲秒脉冲时时输输出出分分输输出出校时校时校时功能切换校时功能切换复位复位秒秒输输出出七段数码管译码器及显示器七段数码管译码器及显示器正常计时时间和定时时间输出选择切换电路正常计时时间和定时时间输出选择切换电路时时输输出出分分输输出出秒秒输输出出VCCK1K1闭合,显示正常计时时间闭合,显示正常计时时间K1断开,显示定时器时间断开,显示定时器时间思考:在正常思考:在正常显示时间时,显示时间时,如

17、何使定时器如何使定时器“”键失效,键失效,以保证在正常以保证在正常计时时定时时计时时定时时间不被修改?间不被修改?正常计时时间和闹铃时间比较器电路连接正常计时“时”信号输出连接正常计时“分”信号输出连接闹铃时间“时”信号输出连接闹铃时间“分”信号输出与门电路两时间相等,输出高电平512Hz周期信号思考:响铃思考:响铃时间为时间为1分钟,分钟,如何保证?如何保证?数字钟电路设计将上一讲中的数字钟包装成一个元件,引脚定义如下图所示。将上一讲中的数字钟包装成一个元件,引脚定义如下图所示。定时器控制电路及定时时间存储电路设计定时器控制电路定时器控制电路复位复位定时时间存储电路定时时间存储电路调时或调分

18、调时或调分选择开关选择开关“”键键分分输输出出时时输输出出定时器控制电定时器控制电路及定时时间路及定时时间存储电路存储电路Ctrl_memoresetk1Up_key“+”键Q_houra3.0Q_hourb1.0Q_minuea3.0Q_minueb2.0定时器控制电路及定时时间存储电路VHDL程序LIBRARY ieee; USE ieee.std_logic_1164.all;ENTITY ctrl_memo ISPORT( reset,k1,up_key: IN STD_LOGIC; -k1高电平为调时,低电平为调分高电平为调时,低电平为调分 Q_hourb : OUT INTEGER

19、 RANGE 0 TO 2;-“时时”高位高位 Q_houra : OUT INTEGER RANGE 0 TO 9;-“时时”低位低位 Q_minueb : OUT INTEGER RANGE 0 TO 5; Q_minuea : OUT INTEGER RANGE 0 TO 9);END ctrl_memo;ARCHITECTURE a OF ctrl_memo IS BEGIN PROCESS(reset,k1,up_key) VARIABLE Q_tmpma: INTEGER RANGE 0 TO 9; VARIABLE Q_tmpmb: INTEGER RANGE 0 TO 5; V

20、ARIABLE Q_tmpha: INTEGER RANGE 0 TO 9; VARIABLE Q_tmphb: INTEGER RANGE 0 TO 2;BEGIN IF reset=0 THEN Q_tmpma:= 0; Q_tmpmb:= 0;Q_tmpha:= 0; Q_tmphb:= 0; ELSIF up_keyevent AND up_key=1 THEN IF k1=1 THEN IF Q_tmphb=2 AND Q_tmpha=3 THEN Q_tmphb:=0; Q_tmpha:=0 ; ELSIF Q_tmpha=9 THEN Q_tmpha:=0; Q_tmphb:=Q

21、_tmphb+1; ELSE Q_tmpha:=Q_tmpha+1; END IF; else IF Q_tmpmb=5 AND Q_tmpma=9 THEN Q_tmpmb:=0; Q_tmpma:=0 ; ELSIF Q_tmpma=9 THEN Q_tmpma:=0; Q_tmpmb:=Q_tmpmb+1; ELSE Q_tmpma:=Q_tmpma+1; END IF; END IF; END IF ; Q_hourb=Q_tmphb; Q_houra=Q_tmpha; Q_minueb=Q_tmpmb; Q_minuea=Q_tmpma; END PROCESS ;END a;正常计

22、时时间和定时时间输出选择切换电路正常计时时间和定时时间输出选择切换电路QHAI5.0正常计时时间和定时时间输出选择切换电路正常计时时间和定时时间输出选择切换电路 NOR_ARM_CTL.VHDk2Q_HAO3.0Q_HBO1.0Q_MAO3.0Q_MBO2.0Q_SAO3.0Q_SBO2.0QSAI6.0QMAI6.0QH_ARM5.0QM_ARM6.0正常时间输入,接时钟输出正常时间输入,接时钟输出闹钟时间输入,接闹钟定时输出闹钟时间输入,接闹钟定时输出K2为高电平时显示正常时间仿真波形仿真波形正常计时时间和定时时间输出选择切换电路 VHDL程序LIBRARY ieee; USE ieee.

23、std_logic_1164.all;ENTITY NOR_ARM_CTL ISPORT( k2: IN STD_LOGIC; QSAI,QMAI,QHAI:IN INTEGER RANGE 0 TO 9; QSBI,QMBI:IN INTEGER RANGE 0 TO 5; QHBI:IN INTEGER RANGE 0 TO 2; QH_ARM_A,QM_ARM_A: IN INTEGER RANGE 0 TO 9; QH_ARM_B: IN INTEGER RANGE 0 TO 2; QM_ARM_B: IN INTEGER RANGE 0 TO 5; Q_HAO,Q_MAO,Q_SAO

24、:OUT INTEGER RANGE 0 TO 9; Q_HBO: OUT INTEGER RANGE 0 TO 2; Q_MBO,Q_SBO : OUT INTEGER RANGE 0 TO 5);END NOR_ARM_CTL;ARCHITECTURE a OF NOR_ARM_CTL IS BEGIN Q_HAO=QHAI WHEN K2=1 ELSE QH_ARM_A; Q_HBO=QHBI WHEN K2=1 ELSE QH_ARM_B; Q_MAO=QMAI WHEN K2=1 ELSE QM_ARM_A; Q_MBO=QMBI WHEN K2=1 ELSE QM_ARM_B; Q

25、_SAO=QSAI WHEN K2=1 ELSE 0; Q_SBO=QSBI WHEN K2=1 ELSE 0;END a;仿真波形仿真波形正常计时时间和闹铃时间比较器电路 BIJIAOQI.VHD与门电路两时间相等,输出高电平512Hz周期信号正常计时时间和闹铃时间比较器电路设计clk0speakQH_AQH_BQM_AQM_BHARM_AHARM_BMARM_AMARM_BY正常计时时间和闹铃时间比较器电路VHDL程序LIBRARY ieee; USE ieee.std_logic_1164.all;ENTITY BIJIAOQI ISPORT( CLk0: IN STD_LOGIC; Q

26、H_A,QM_A: IN INTEGER RANGE 0 TO 9; QH_B: IN INTEGER RANGE 0 TO 2; QM_B: IN INTEGER RANGE 0 TO 5; HARM_A,MARM_A: IN INTEGER RANGE 0 TO 9; HARM_B: IN INTEGER RANGE 0 TO 2; MARM_B: IN INTEGER RANGE 0 TO 5; SPEAK: OUT STD_LOGIC);END BIJIAOQI;ARCHITECTURE a OF BIJIAOQI IS SIGNAL Y: STD_LOGIC; BEGIN SPEAK

27、=CLK0 AND Y; Y=1 WHEN (QH_A=HARM_A) AND (QM_A=MARM_A) AND (QH_B=HARM_B) AND (QM_B=MARM_B) ELSE 0;END a;仿真波形仿真波形总电路图总电路图三、校园打铃系统功能电路设计三、校园打铃系统功能电路设计方案二:地址发生器及外置存储器方式方案二:地址发生器及外置存储器方式方案一:直接数据比较方法方案一:直接数据比较方法方案一:直接数据比较方法方案一:直接数据比较方法春季作息时间夏季作息时间6:50起床6:40起床7:40预备7:30预备7:50第一节上课7:40第一节上课8:35第一节下课8:25第一节下

28、课8:45第二节上课8:35第二节上课9:30第二节下课9:20第二节下课9:50第三节上课9:40第三节上课10:35第三节下课10:25第三节下课10:45第四节上课10:35第四节上课11:30第四节下课11:20第四节下课14:00预备14:20预备14:10下午第一节上课14:30下午第一节上课14:55下午第一节下课15:15下午第一节下课15:05下午第二节上课15:25下午第二节上课15:50下午第二节下课16:10下午第二节下课16:00下午第三节上课 16:20下午第三节上课16:45下午第三节下课 17:05下午第三节下课16:55下午第四节上课 17:15下午第四节上课

29、17:40下午第四节下课 18:00下午第四节下课19:00晚上第一节上课 19:10晚上第一节上课19:45晚上第一节下课 19:55晚上第一节下课19:55晚上第二节上课 20:05晚上第二节上课20:40晚上第二节下课 21:00晚上第二节下课将“时分”并置,得到下列数据:春季作息时间 夏季作息时间065006400740073007500740083008250845083509300920095009401035102510451035113011201400142014101430145515151505152515501610160016201645170516551715174

30、0180019001810194519551955200520402100实现方法:实现方法: 将数字钟输出的时间(时和分)逐一与上表中的数据进行比较,将数字钟输出的时间(时和分)逐一与上表中的数据进行比较,如果相等,则如果相等,则Q_Y输出高电平,否则输出低电平。输出高电平,否则输出低电平。基本数字钟电路基本数字钟电路秒脉冲秒脉冲时时输输出出分分输输出出校时校时校时功能切换校时功能切换复位复位秒秒输输出出时间比较器(时间比较器(comp_time)JK交流电铃220V5VQ_YR3K高电平:春季低电平:夏季K3Q_HAQ_HBQ_MAQ_MB译码及显示译码及显示时间比较器的时间比较器的VHD

31、L程序(程序(COMP_TIME.VHD)LIBRARY ieee; USE ieee.std_logic_1164.all;ENTITY COMP_TIME ISPORT( K3: IN STD_LOGIC; Q_HA,Q_MA: IN STD_LOGIC_VECTOR(3 DOWNTO 0); Q_HB: IN STD_LOGIC_VECTOR(1 DOWNTO 0); Q_MB: IN STD_LOGIC_VECTOR(2 DOWNTO 0); Q_Y: OUT STD_LOGIC);END COMP_TIME;ARCHITECTURE a OF COMP_TIME IS SIGNAL

32、QTIME:STD_LOGIC_VECTOR(12 DOWNTO 0); BEGIN QTIME Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y Q_Y=0; END CASE; END IF; END PROCESS; END a;关于电铃响铃时间关于电铃响铃时间15秒的处理方法秒的处理方法:说明:因为比较器的输出说明:因为比较器的输出QY高电平时间为高电平时间为1分钟,如果不作处理,则电铃分钟,如果不作处理,则电铃将响将响1分钟。分钟。处理方法:处理方法:1、

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- T/CACE 067-2022废弃电器电子产品零部件梯次利用技术规范

- 腰椎骨折术前健康教育

- 无机结合料稳定材料配合比设计80课件

- 疫情校园封闭心理健康教育

- 生气汤:健康领域的心理教育活动

- T/BULA 0001-2023道路和隧道照明用LED灯具

- 2025年物联网设备安全漏洞检测与防护技术发展趋势研究报告

- 2025年教育信息化2.0背景下教师团队建设与协作模式研究

- 直肠癌常见的护理问题

- DB37/T 4444-2021城市轨道交通列车驾驶员作业规范

- 人工智能在电力系统中的应用前景

- 双膝骨性关节炎课件查房

- 国家开放大学-传感器与测试技术实验报告(实验成绩)

- 大众电子助力转向EPS 双齿轮电动助力转向系统

- 《传媒翻译》课件

- 脑卒中患者血压及血糖管理

- 印刷企业安全生产检查表

- 能源费用托管型合同能源管理项目

- 2021-2022学年重庆市沙坪坝区八年级(下)期末语文试卷(解析版)2021

- 静配中心基础知识课件

- 南非介绍课件

评论

0/150

提交评论