版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、EDA课程设计多路彩灯控制设计前言本次课程设计的主要目的是通过电子设计自动化的设计,掌握FPGA应用系统的开发过程,进一步理解FPGA应用系统的工作原理。本课程设计设计了一个多路彩灯控制器,十六种彩灯能循环变化,有清零开关,可以变化彩灯闪动频率即是可以选择快慢两种节拍。整个系统有三个输入信号,分别为控制快慢的信号OPT,复位清零信号CLR,输出信号是16路彩灯输出状态。最后按照FPGA的开发流程和VHDL语言建模、仿真、综合、下载、适配,用EDA6000实验箱上的FPGA系统实现了相应的功能。通过这次课程设计更清楚的理解了VHDL程序的描述语言,能进行简单程序的编写和仿真。一系统设计要求 设计

2、一个多路彩灯控制器,十六种彩灯能循环变化,有清零开关,可以变化彩灯闪动频率即是可以选择快慢两种节拍。二.设计方案整个系统有三个输入信号,分别为控制快慢的信号OPT,复位清零信号CLR,输出信号是16路彩灯输出状态。系统框图如: 主要模块组成:时序控制电路模块和显示电路模块,时序控制电路是根据输入信号的设置得到相应的输出信号,并将此信号作为显示电路的时钟信号;显示电路输入时钟信号的周期,有规律的输出设定的六种彩灯变化类型。三.模块设计时序控制模块:CLK_IN为输入时钟信号,电路在时钟上升沿变化;CLR为复位清零信号,高电平有效,一旦有效时,电路无条件的回到初始状态;chose_key为频率快慢

3、选择信号,低电平节奏快,高电平节奏慢;CLK为输出信号,CLR有效时输出为零,否则,随chose_key信号的变化而改变。我们假设时序控制电路所产生的控制时钟信号的快慢两种节奏分别为输入时钟信号频率的1/4和1/8,因而输出时钟控制信号可以通过对输入时钟的计数来获得。当chose_key为低电平时,输出没经过两个时钟周期进行翻转,实现四分频的快节奏;当chose_key为高电平时,输出每经过四个时钟周期进行翻转,实现把八分频的慢节奏。显示控制电路的模块框图如图所示,输入信号clk和的定义与时序控制电路一样,输入信号led15.0能够循环输出16路彩灯16种不同状态的花型。对状态的所对应的彩灯输

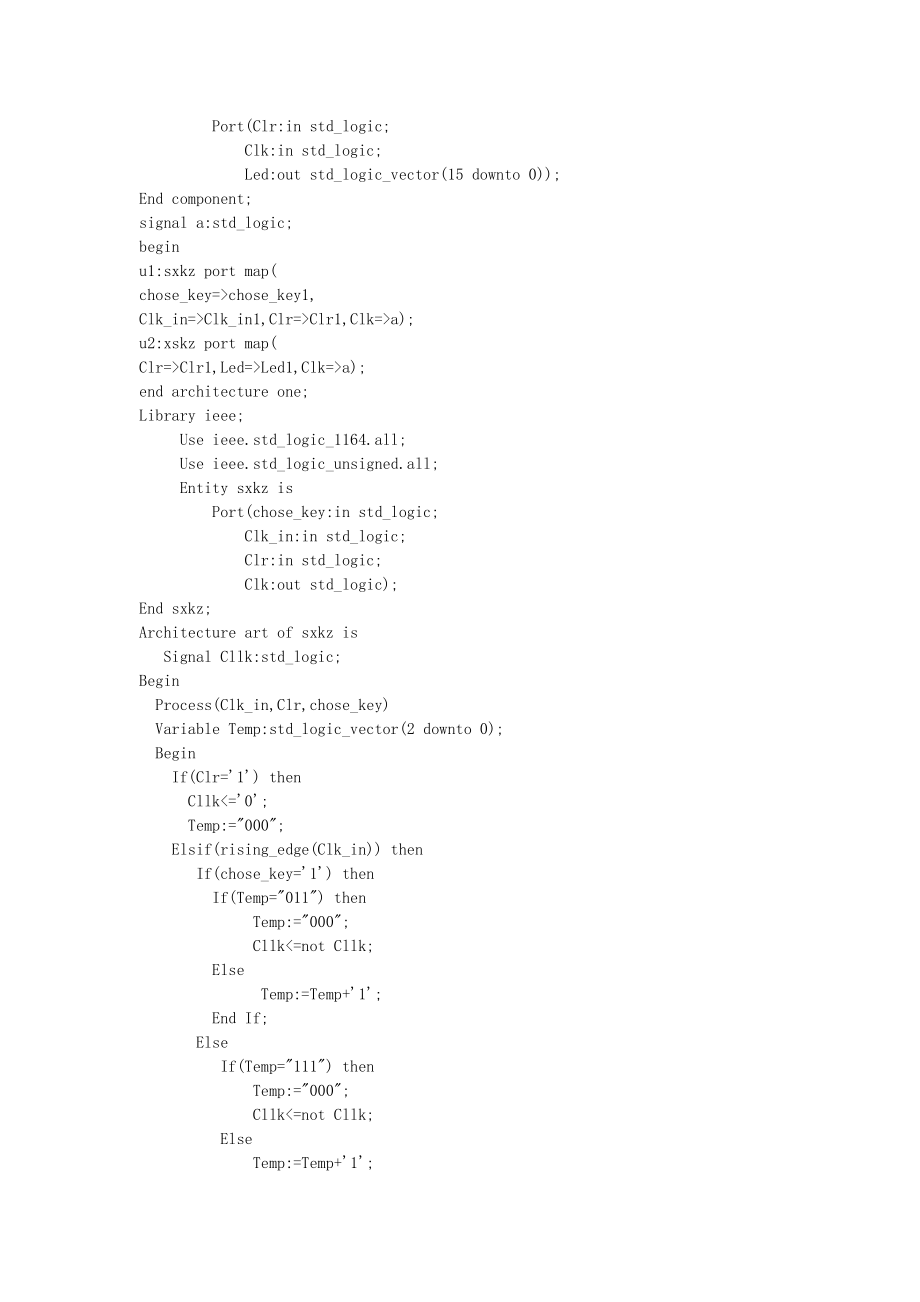

4、出花型定义如下:S0:0000000000000000 S1:多路彩灯在多种花型之间的转换可以通过状态机实现,当复位信号clr有效时,彩灯恢复初始状态s0,否则,每个时钟周期,状态都将向下一个状态发生改变,并对应输出的花型,这里的时钟周期即时时序控制电路模块产生的输出信号,它根据chose_key信号的不同取值得到两种快慢不同的时钟频率。四.序控制电路模块程序如下:Library ieee; Use ieee.std_logic_1164.all; Use ieee.std_logic_unsigned.all; Entity CD is Port(chose_key1:in std_logi

5、c; Clk_in1:in std_logic; Clr1:in std_logic; Led1:out std_logic_vector(15 downto 0); End CD; Architecture one of CD iscomponent sxkzPort(chose_key:in std_logic; Clk_in:in std_logic; Clr:in std_logic; Clk:out std_logic);End component; component xskz Port(Clr:in std_logic; Clk:in std_logic; Led:out std

6、_logic_vector(15 downto 0);End component;signal a:std_logic;beginu1:sxkz port map(chose_key=>chose_key1,Clk_in=>Clk_in1,Clr=>Clr1,Clk=>a);u2:xskz port map(Clr=>Clr1,Led=>Led1,Clk=>a);end architecture one;Library ieee; Use ieee.std_logic_1164.all; Use ieee.std_logic_unsigned.all;

7、 Entity sxkz is Port(chose_key:in std_logic; Clk_in:in std_logic; Clr:in std_logic; Clk:out std_logic);End sxkz;Architecture art of sxkz is Signal Cllk:std_logic;Begin Process(Clk_in,Clr,chose_key) Variable Temp:std_logic_vector(2 downto 0); Begin If(Clr='1') then Cllk<='0' Temp:=

8、"000" Elsif(rising_edge(Clk_in) then If(chose_key='1') then If(Temp="011") then Temp:="000" Cllk<=not Cllk; Else Temp:=Temp+'1' End If; Else If(Temp="111") then Temp:="000" Cllk<=not Cllk; Else Temp:=Temp+'1' End If; End

9、 If; End If; End process; Clk<=Cllk; End art;Library ieee;Use ieee.std_logic_1164.all; Use ieee.std_logic_unsigned.all; Entity xskz is Port( Clr:in std_logic; Clk:in std_logic; Led:out std_logic_vector(15 downto 0);End xskz;Architecture art of xskz is Type state is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s

10、10,s11,s12,s13,s14,s15,s16); Signal current_state:state; Signal flower:std_logic_vector(15 downto 0); Begin Process(Clr,Clk) Begin If(Clr='1') then current_state<=s0; elsif(rising_edge(Clk) then case current_state is when s0=> flower<="ZZZZZZZZZZZZZZZZ" current_state<=s

11、1; when s1=> flower<=f1; current_state<=s2; when s2=> flower<=f2; current_state<=s3; when s3=> flower<=f3; current_state<=s4; when s4=> flower<=f4; current_state<=s5; when s5=> flower<=f5; current_state<=s6; when s6=> flower<=f6; current_state<=s

12、7; when s7=> flower<=f7; current_state<=s8; when s8=> flower<=f8; current_state<=s9; when s9=> flower<=f9; current_state<=s10; when s10=> flower<=f10; current_state<=s11; when s11=> flower<=f11; current_state<=s12; when s12=> flower<=f12; current_st

13、ate<=s13; when s13=> flower<=f13; current_state<=s14; when s14=> flower<=f14; current_state<=s15; when s15=> flower<=f15; current_state<=s16; when s16=> flower<=f16; current_state<=s1; end case; end if; end process; led<=flower; end art;时序模块电路程序如下:显示模块电路程序:顶

14、出模块设计程序:其状态图:时序控制模块仿真波形:从图中可以看出,当复位信号为高电平时,电路时钟输出清零,当快慢信号chose_key1为低电平时,时序控制电路四分频起作用,当快慢信号chose_key1为高电平时,时序控制电路八分频起作用,仿真结果符合电路要求。显示模块仿真波形:当复位信号有效时彩灯输出为零,否则,显示电路在十六种不同状态间转换。多路彩灯控制仿真波形:从图中可以看出当chose_key1为高电平时彩灯状态转换慢,为低电平时转换要快,当复位信号有效时,所用输出都清零。伟福6000仿真图:综上所述,本次设计实现了设计要求中的要求。五.系统设计工作进程安排: 17周 周一、二,查找和

15、准备了相关设计材料,熟悉过去学过的FPGA芯片、VHDL 语言和EDA环境相关知识 周三、四、五,进行相应的程序设计 18周 周一,在实验室熟悉EDA的环境使用,熟悉相关设计软件 周二、三,在实验室上机,使用EDA6000实验箱调试程序 周四,老师验收设计六.心得体会本次设计的课题是彩灯控制器的设计,当拿到这个课题的时候经过分析就知道关键是计数器和分频器的使用,分频的方法有很多种,对于同一种功能的实现,用VHDL可以采用多种方式进行描述,每种方式之间各有优劣,本次设计只采用了其中较简单的一种,应尽量用最简洁的语言写出所需功能的程序。通过这次课程设计对技术有了更进一步的熟悉,VHDL 语言和语言

16、等其他语言还是有很大的区别。VHDL是EDA技术的重要组成部分,其具有与具体硬件电路无关和与设计平台无关的特性,并且具有良好的电路行为描述和系统描述的能力,并在语言易读性和层次化、结构化设计方面,表现了强大的生命力和应用潜力。其主要的也是最大的优点就在于设计者可以专心致力于其功能的实现,而不需要对不影响功能的与工艺有关的因素花费过多的时间和精力。在实际操作中发现设计和课本上的知识有很大联系,但又高于课本,一个简单的原理要把它应用以及和其他功能综合起来就有些困难。通过设计也巩固了我们的书本知识以及通过借阅书籍和上网查找资料,也丰富了自己对的了解。不过本次设计也存在一些不足,暴露了自己对的掌握还有所欠缺。在设计过程中,分频分的太大,频率太小的话,频率太大的话,数码管显示

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 老字号品牌振兴计划实施方案(参考范文)

- 《少年的你》观后感(15篇)

- 河道生态修复工程可行性研究报告

- 工厂建设项目立项报告

- 形势与政策关注国家大事培养家国情怀

- 新疆乌鲁木齐市实验学校2023-2024学年高三上学期1月月考物理含解析

- 不跟陌生人走安全教育教案

- 广东省部分学校2023-2024学年高三上学期11月联考地理含解析

- 心理安全小班课件教案

- 杭州职业技术学院《学前游戏论》2023-2024学年第二学期期末试卷

- 14.第十四周 绷紧“防震弦”奏响“安全曲”

- 2025年湘教版初中地理七年级下册重点知识点梳理与归纳

- 旅游行业安全管理概述

- 中国商业航天研究报告

- 胎漏、堕胎、滑胎、小产中医护理常规

- 红色卡通风全国助残日PPT模板

- 《城市综合防灾规划》教学大纲

- SimMarketing营销模拟实验室操作篇

- 阀门螺栓使用对照表

- 电诊断在康复医学中的应用ppt课件

- HDPE塑料检查井施工工艺

评论

0/150

提交评论