版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、1数字逻辑电路数字逻辑电路组合逻辑电路组合逻辑电路时序逻辑电路时序逻辑电路 输出状态输出状态只只决定于决定于当前当前时刻各输入时刻各输入状态的组合,而与电路状态的组合,而与电路先前先前状态状态无关无关(无记忆功能无记忆功能) 。 输出状态输出状态不仅不仅决定于决定于当前当前时刻各输入时刻各输入状态的组合,而且还与电路状态的组合,而且还与电路先前先前状态状态有关有关(有记忆功能有记忆功能) 。第第21章章 触发器和时序逻辑电路触发器和时序逻辑电路门电路门电路是是组合电路组合电路的基本单元的基本单元触发器触发器是是时序电路时序电路的基本单元的基本单元按按功能功能分类:分类:R-S触发器、触发器、D

2、型触发器、型触发器、JK触发器、触发器、T型触发器等。型触发器等。按按稳定工作状态稳定工作状态:双双稳态、稳态、单单稳态、稳态、无无稳态触发器(多谐振荡器)稳态触发器(多谐振荡器)按按结构结构分类:基本型、同步型、主从型、维持阻塞分类:基本型、同步型、主从型、维持阻塞型型。2QDRDS&Q反馈反馈两个输入端两个输入端两个输出端两个输出端SRQQ逻辑图逻辑图逻辑符号逻辑符号Q=1,Q =0时,称触发器处于置位状态(时,称触发器处于置位状态(1态);态);Q=0,Q=1时,称触发器处于复位状态(时,称触发器处于复位状态(0态)。态)。现态现态输入信号作用前的状态,用输入信号作用前的状态,用

3、Qn和和Qn(或或Q、Q)表示;表示;次态次态输入信号作用后的状态,用输入信号作用后的状态,用Qn+1和和Qn+1表示。表示。 SD置置1端或置位端或置位(SET)端;端;RD置置0或复位或复位(RESET)端。端。 21.1.1 RS触发器触发器21.1 双稳态触发器双稳态触发器 1. 基本基本RS触发器触发器SDRD3&QQDRDS(1) 输入输入RD=0, SD=1时时1001输出:输出:10QQ(2)输入)输入RD=1, SD=0时时0110&a&bQQDRDS输出:输出:01QQ触发信号触发信号输出端状态改变时输入端所加的有效信号。输出端状态改变时输入端所加的

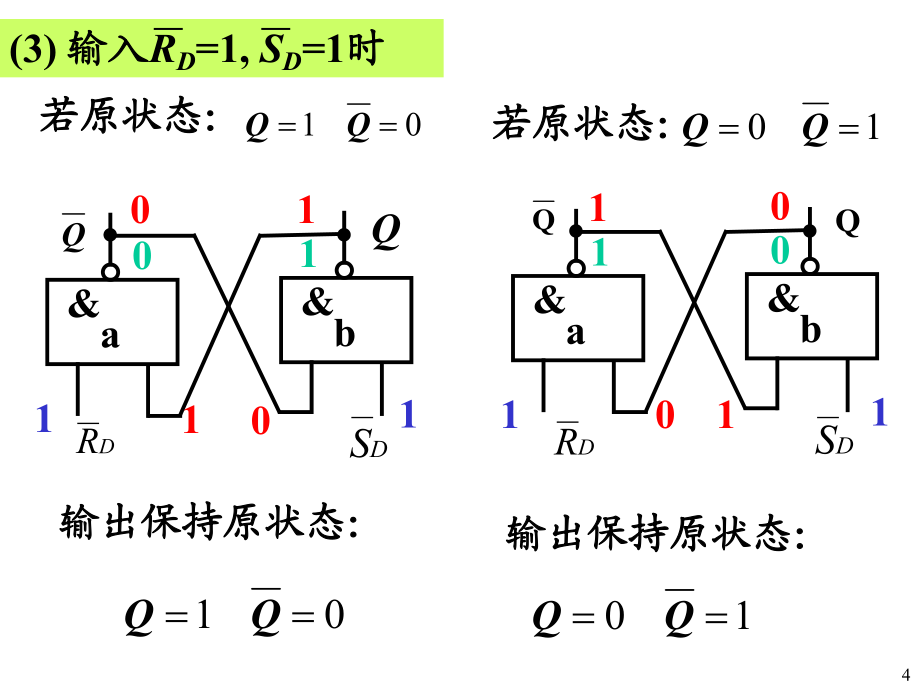

4、有效信号。翻转翻转输出端状态的转换过程。输出端状态的转换过程。基本基本RS触发器又称为置触发器又称为置0置置1触发器,或置位复位触发器。触发器,或置位复位触发器。4若原状态:若原状态:10111001输出保持原状态:输出保持原状态:01QQ01QQ&a&bQQDRDS01110110&a&bQQDRDS若原状态:若原状态:10QQ输出保持原状态:输出保持原状态:10QQ(3) 输入输入RD=1, SD=1时时5(4) 输入输入RD=0, SD=0时时&a&bQQDRDS001111若若a门快,门快,=0,Q=1Q若若b门快,门快, Q=0,Q=1

5、当当RD=SD=0同时变为同时变为1时,翻转快的门输出变为时,翻转快的门输出变为0,另,另一个不得翻转。一个不得翻转。-不定状态,应当避免。不定状态,应当避免。6SRQQ逻辑符号逻辑符号SDRD逻辑状态表01不变不定10100110 SDRDQn+1简化的逻辑状态表7不定QRS例:基本例:基本RS触发器的触发器的R、S端波形如下,画出端波形如下,画出Q端波形。端波形。不定Q8由或非门组成的基本由或非门组成的基本RS触发器触发器901不变不定 SDRDQn+1101001101011(2)可控)可控RS触发器触发器&QQ&RSCPSDRDSRQQSCPRDDCSRQ不定(Cloc

6、k-Pulse)CP R S Q 0 保保 持持 1 0 0 保保 持持 1 0 1 1 0 1 1 0 0 1 1 1 1 不确定不确定 Q CP12 SRQn + 100110101Qn01不 定1321.1.2 JK触发器触发器逻辑状态表14SRQQJCPKDDnn1nQKQJQ+ + + +15SRQQDCDD21.1.3 D触发器触发器QCDCPQn+1 = D164、触发器逻辑功能的转换、触发器逻辑功能的转换(1)将)将JK触发器转换为触发器转换为D触发器触发器SRQQJCKDD1D(2)将)将JK触发器转换为触发器转换为T触发器触发器SRQQJCKDDTTQn+101QnQn17

7、(3)将)将D触发器转换为触发器转换为T触发器触发器SRQQDCDDn+1Qn=Q181921.1.6. 在下图中,试着画出Q1和Q2端的波形,时钟的波形如下所示。时钟的频率为4000Hz,那么Q1和Q2的频率各位多少?2021.1.7. 在下图中,试着画出Q1和Q2端的波形,时钟的波形如下所示。Q1和Q2的初始时刻为0。2121.1.8. 如图所示电路是一个可以产生几种脉冲波形的信号发生器。试从所给出的时钟脉冲画出三个输出端口的波形。设初始状态为0。2221.1.9. 试分析下图所示电路,画出Y1和Y2的波形,并与时钟脉冲CP比较,说明电路的功能。设初始状态为0。23&1A11B21Y342B52Y6GND72A1098111213144B 4A 4Y3A 3Y3BVCC&74LS00引脚分布图引脚分布图21.1.10. 下图是一

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2026年汕尾市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)含答案详解(巩固)

- 贵阳市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)含答案详解(满分必刷)

- 十堰市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)含答案详解(培优a卷)

- 九江市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)含答案详解(研优卷)

- 湛江市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)及答案详解(易错题)

- 大连市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)含答案详解(b卷)

- 佛山市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)含答案详解(培优)

- 鹤壁市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)含答案详解(综合题)

- 宿迁市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)含答案详解(轻巧夺冠)

- 周口市农村信用社联合社秋季校园招聘笔试备考题库(浓缩500题)附答案详解(能力提升)

- 管道设备安装培训课件模板

- 应急救援课件8

- 2023年DCA考试试题题库

- GB/T 5972-2023起重机钢丝绳保养、维护、检验和报废

- 华为BEM战略解码体系完整版

- 深圳港危险品海运出口流程

- 设计质量保证措施三篇

- 《以奋斗者为本》摘要

- GB/T 7714-2015信息与文献参考文献著录规则

- 公共事业管理概论期末考试试题

- CB/T 3780-1997管子吊架

评论

0/150

提交评论