版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、第二章 运算方法和运算器学习重点l 数据与文字的表示l 定点加法、减法运算l 定点运算器的组成l 浮点运算的步骤2.1 数据与文字的表示方法 数据格式计算机中使用的数据可分成两大类:数值数据:数字数据的表示(定点、浮点)符号数据:非数字符号的表示(ASCII、汉字、图形等)数值数据的表示格式有定点数、浮点数两种1.定点数的表示方法小数点的位置固定不变,通常表示成纯小数或纯整数。用n+1位字表示定点数 X, x= xnxn-1xn-2x1x0纯小数时表示范围:0X1-2-n纯整数时表示范围:0X2n-12.浮点数的表示方法 任意进制数N表示:N=ReM M为尾数,数的精度; e为指数(整数),数

2、的范围; R为基数,二进制为2,十进制为10; 浮点数由阶码、尾数及其符号位组成。规格化:若不对浮点数的表示作出明确规定,同一个浮点数的表示就不是惟一的。例如:0.010100102110.00101001021000.1010010210IEEE754标准(规定了浮点数的表示格式,运算规则等)规则规定了32位和64位两种基本格式规则中,尾数用原码,指数用移码(便于对阶和比较),基数为2尾数域的最高有效位为1,称为浮点数的规格化表示。32位的浮点数S数的符号位,1位,在最高位,“0”表示正数,“1”表示负数。E是阶码,8位,采用移码表示。移码比较大小方便。M是尾数,23位,在低位部分,采用纯小

3、数表示。规格化的浮点数尾数域最左位(最高有效位)总是1, 故这一位经常不予存储,而认为隐藏在小数点的左边(1.M) 。采用这种方式时,将浮点数的指数真值e变成阶码E时,应将指数e加上一个固定的偏移值127(01111111),即E=e+127。一个规格化的32位浮点数x的真值表示为x=(-1)S(1.M)2E-127设e=E-127x=(-1)S(1.M)2e例1若浮点数x的754标准存储格式为(41360000)16,求其浮点数的十进制数值。解:将16进制数展开后,可得二制数格式为0 10000010 011 0110 0000 0000 0000 0000S 阶码(8位) 尾数(23位)指

4、数e=阶码E-127=10000010-01111111=00000011=(3)10包括隐藏位1的尾数M=1.011 0110 0000 0000 0000 0000=1.011011于是有x=(-1)S1.M2e=+(1.011011)23=+1011.011=(11.375)10例2将数(20.59375)10转换成754标准的32位浮点数的二进制存储格式。解:首先分别将整数和小数部分转换成二进制数: 20.59375=10100.10011然后移动小数点,使其在第1,2位之间 10100.10011=1.01001001124e=4于是得到: E=e+127=4+127=131S=0,

5、 E=131=10000011, M=010010011最后得到32位浮点数的二进制存储格式为:41A4C000)16真值x为零表示:当阶码E为全0且尾数M也为全0时的值,结合符号位S为0或1,有正零和负零之分。真值x为无穷大表示:当阶码E为全1且尾数M为全0时,结合符号位S为0或1,也有+和-之分。这样在32位浮点数表示中,要除去E用全0和全1(255)表示零和无穷大的特殊情况,对于规格化浮点数,E的范围变为1到254,因为E=e+127,所以真正的指数值e则为-126到+127。因此32位浮点数表示的绝对值的范围是10-381038(以10的幂表示)。64位的浮点数中符号位1位,阶码域11

6、位,尾数域52位,指数偏移值是1023。因此规格化的64位浮点数x的真值为:x=(-1)S(1.M)2E-1023 e=E-1023浮点数所表示的范围远比定点数大。一台计算机中究竟采用定点表示还是浮点表示,要根据计算机的使用条件来确定。一般在高档微机以上的计算机中同时采用定点、浮点表示,由使用者进行选择。而单片机中多采用定点表示。机器码:机器中表示的数, 要解决在计算机内部数的正、负符号和小数点运算问题。原码、反码、补码、移码例7将十进制真值(127,1,0,1,127)列表表示成二进制数及原码、反码、补码、移码值。例8设机器字长16位,定点表示,尾数15位,数符1位,问:(1)定点原码整数表

7、示时,最大正数是多少?最小负数是多少?(2)定点原码小数表示时,最大正数是多少?最小负数是多少?定点原码整数表示最大正数值(215-1)10(32767)10最小负数值(215-1)10(32767)10定点原码小数表示 最大正数值(1-2-15)10(0.111.11)2最小负数值(1-2-15)10(0.111.11)2数字编码输入的优点是无重码,且输入码与内部编码的转换比较方便,缺点是代码难以记忆。拼音码是以汉字拼音为基础的输入方法。使用简单方便,但汉字同音字太多,输入重码率很高,同音字选择影响了输入速度。 为了加快输入速度,在上述方法基础上,发展了词组输入、联想输入等多种快速输入方法。

8、更理想的输入方式是利用语音或图象识别技术“自动”将拼音或文本输入到计算机内,并将其自动转换为机内代码表示。目前这种理想已经成为现实,如语音输入、手写输入、OCR等。 汉字内码汉字内码是用于汉字信息的存储、交换、检索等操作的机内代码,一般采用两个字节表示。汉字机内代码中两个字节的最高位均规定为“1”。(一级汉字3755个,二级汉字3008个) 注意:有些系统中字节的最高位用于奇偶校验,此情况下用三个字节表示汉字内码。 校验码校验码(只介绍奇偶校验码)引入:信息传输和处理过程中受到干扰和故障,容易出错。解决方法:是在有效信息中加入一些冗余信息(校验位)奇偶校验位定义缺点其它校验方法还有Hammin

9、g,CRC2.2定点加法、减法运算 补码加减法补码加法公式:x+y补=x补+y补补码减法公式:x-y补=x补+-y补该公式将减法转变为加法如何求-y补?y=0.0111 y补=0.0111-y补=1.1001例: x=-0.1011,y=0.0111,求x+y=?解: x补=1.0101 y补=0.0111x+y补=x补+y补 =1.0101+0.0111=1.1100x+y=-0.0100例: x=0.11011,y=-0.11111,求x-y=?解: x补=0.11011 y补=1.00001 -y补=0.11111x-y补=x补+-y补=1.11010课堂练习例: x0.1011, y0

10、.1001,求x+y补=?例: x0.1101,y0.1011,求x+y 补=? 溢出的检测可能产生溢出的情况两正数加,变负数,上溢(大于机器所能表示的最大数)两负数加,变正数,下溢(小于机器所能表示的最小数)双符号位法(参与加减运算的数采用变形补码表示)Sf1 Sf20 0正确(正数)01上溢10下溢11正确(负数)Sf1和Sf2相同表示正确的符号,逻辑表达式为V=Sf1Sf2,可以用异或门来实现单符号位法Cf C000正确01上溢10下溢11正确V=CfC0 其中Cf为符号位产生的进位,C0为最高有效位产生检验举例:0.1100, 0.1000,求 0.1100, 0.1000,求 结果出

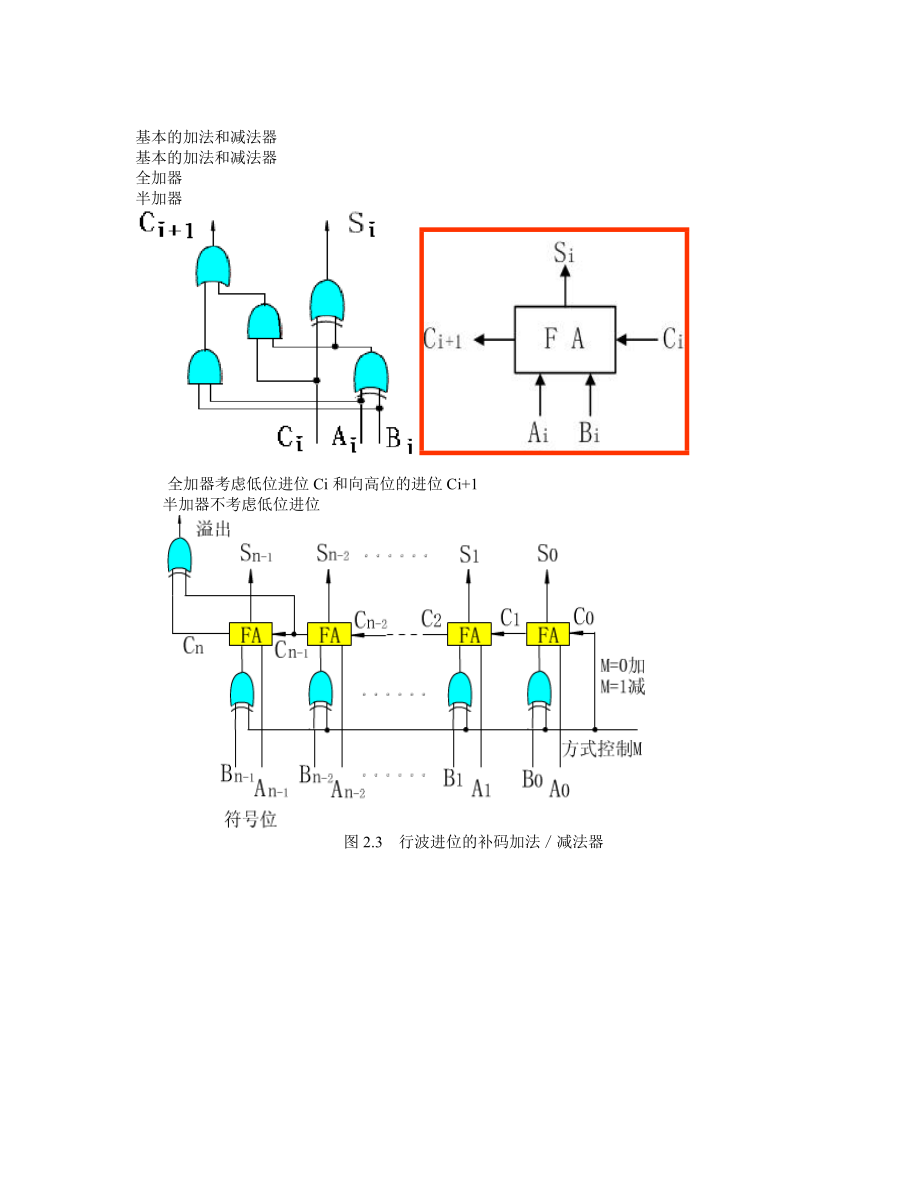

11、现了01或10的情况就为溢出基本的加法和减法器基本的加法和减法器全加器半加器全加器考虑低位进位Ci和向高位的进位Ci+1半加器不考虑低位进位图2.3行波进位的补码加法减法器2.3 定点乘法运算乘法实现方法l 在现有的加法和减法器的基础上增加适当的线路及控制逻辑可以实现l 用LSI和VLSI工艺实现专用的乘法器 LSI (Large-scale integration大规模集成电路)l 编制子程序(单片机等低端机器) 原码并行乘法人工算法与机器算法的同异性 由加法器完成乘法运算需要如下改进n n位乘n位积可能为2n位. n 乘积的最后是所有部分积之和,有n个数相加,而FA只有两个输入端 方法一:

12、硬件实现方法(串行的“加法和移位”),硬件结构简单,速度太慢(已经淘汰). 方法二:不带符号位的阵列乘法器要实现n位n位时,需要n(n1)个全加器和n2个“与”门。 图2.4 mn位不带符号的阵列乘法器逻辑图带符号位的阵列乘法器计算机中定点数通常用补码表示,而前面介绍的不带符号阵列乘法器是用原码计算乘法的,为了能进行补码乘法,需要在计算乘法之前和之后增加求补电路。原理:算前求补乘法器算后求补求补电路工作特点E=0时,输入和输出相等E=1时,则从数最右端往左边扫描,直到第一个1的时候,该位和右边各位保持不变0A=A,左边各数值位按位取反1A=A例17 设15,13,用带求补器的原码阵列乘法器求出

13、乘积?解: 设最高位为符号位,则输入数据为原 01111 原 11101 符号位单独考虑,算前求补级后 |1111,|1101 算后经求补级输出并加上乘积符号位1,则原码乘积值为111000011。换算成二进制数真值是 (11000011)2=(-195)10十进制数验证:15(13)195相等。2.4定点运算器的组成2.4.1 多功能算术/逻辑运算单元(ALU)一位全加器(FA)的逻辑表达式为FiXiYiCn+i (2.30) Cn+i+1XiYiYiCn+iCn+iXi4位ALU图2.10ALU的逻辑结构原理框图问题:片内是串行进位还是并行进位?4位之间采用先行进位公式,根据式(2.30)

14、,每一位的进位公式可递推如下:第0位向第1位的进位公式为 Cn1Y0X0Cn其中Cn是向第0位(末位)的进位。第1位向第2位的进位公式为 Cn2Y1X1Cn1 Y1Y0X1X0X1Cn第2位向第3位的进位公式为 Cn3Y2X2Cn2 Y2Y1X1Y0X1X2X0X1X2Cn第3位的进位输出(即整个4位运算进位输出)公式为Cn4Y3X3Cn3Y3Y2X3Y1X2X3Y0X1X2X3X0X1X2X3Cn设GY3Y2X3Y1X2X3Y0X1X2X3PX0X1X2X3 则 Cn4GPCn 这样,对一片ALU来说,可有三个进位输出。其中G称为进位发生输出,P称为进位传送输出。在电路中多加这两个进位输出的

15、目的,是为了便于实现多片(组)ALU之间的先行进位,为此还需一个配合电路,称之为先行进位发生器(CLA)74181ALU逻辑电路图(总体)74181ALU逻辑电路图(总体)表2.5 74181ALU算术/逻辑运算功能表设计16位ALUCn+4=G0+P0CnCn+8=G1+P1Cn+4Cn+12=G2+P2Cn+8Cn+16=G3+P3Cn+12片内先行进位,片间串行进位Cn+4=G0+P0Cn Cn+8=G1+P1Cn+4=G1+G0P1+P0P1CnCn+12=G2+P2Cn+8=G2+G1P2+G0P1P2+P0P1P2Cn Cn+16=G3+P3Cn+12=G3+G2P3+G1P2P3+G0P1P2P3+P0P1P2P3Cn=G*+P*CnG*为成组先行进位发生输出P*为成组先行进位传送输出成组先行进位部件CLA的逻辑图16位先行进位ALU图2.13用两个16位全先行进位部件级联组成的32位ALU三态门组成的双向数据总线2.5浮点

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025年智能化微型农业设备开发项目可行性研究报告

- 2025年虚拟现实在旅游行业应用可行性研究报告

- 2025年赛事经济开发项目可行性研究报告

- 2025年传统产业智能化转型可行性研究报告

- 2025年国际贸易电子商务平台构建项目可行性研究报告

- 人才入股协议书

- 供应加工协议书

- 球馆管理合同范本

- 兴县2024山西吕梁兴县事业单位校园招聘9人笔试历年参考题库典型考点附带答案详解(3卷合一)

- 妇产科护士笔试考试题含答案

- 2025广西公需科目培训考试答案(90分)一区两地一园一通道建设人工智能时代的机遇与挑战

- 酸洗钝化工安全教育培训手册

- 汽车发动机测试题(含答案)

- IPC6012DA中英文版刚性印制板的鉴定及性能规范汽车要求附件

- 消除母婴三病传播培训课件

- 学校餐费退费管理制度

- T/CUPTA 010-2022共享(电)单车停放规范

- 设备修理工培训体系

- 《社区营养健康》课件

- DB33T 2455-2022 森林康养建设规范

- 北师大版数学三年级上册课件 乘法 乘火车-课件01

评论

0/150

提交评论