版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

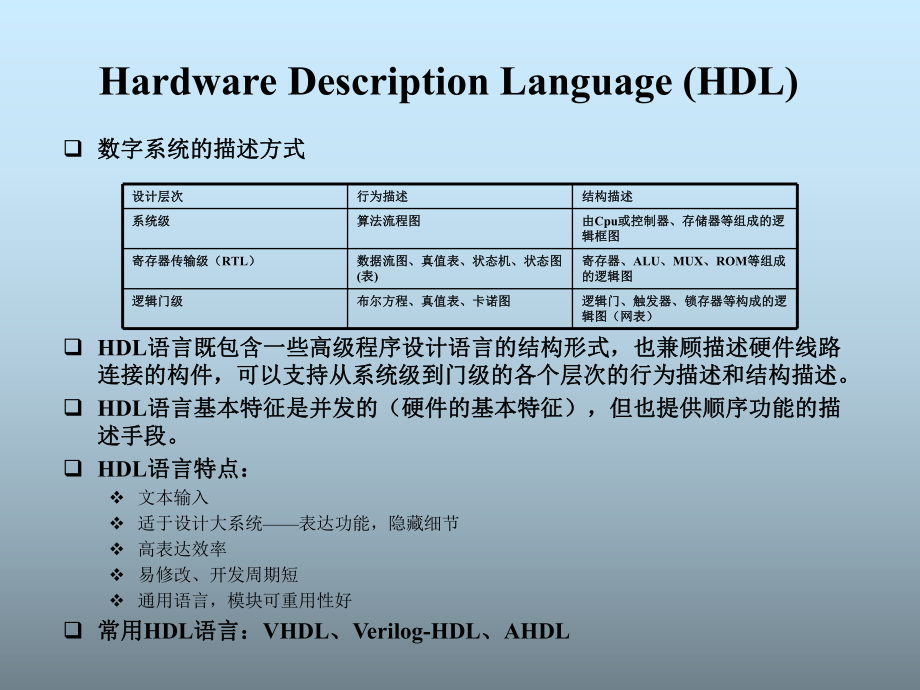

1、可编程逻辑电路设计教学组可编程逻辑电路设计教学组二二七年七年Hardware Description Language (HDL)q 数字系统的描述方式数字系统的描述方式q HDL语言既包含一些高级程序设计语言的结构形式,也兼顾描述硬件线路语言既包含一些高级程序设计语言的结构形式,也兼顾描述硬件线路连接的构件,可以支持从系统级到门级的各个层次的行为描述和结构描述。连接的构件,可以支持从系统级到门级的各个层次的行为描述和结构描述。q HDL语言基本特征是并发的(硬件的基本特征),但也提供顺序功能的描语言基本特征是并发的(硬件的基本特征),但也提供顺序功能的描述手段。述手段。q HDL语言特点:语

2、言特点:v 文本输入v 适于设计大系统表达功能,隐藏细节v 高表达效率v 易修改、开发周期短v 通用语言,模块可重用性好q 常用常用HDL语言:语言:VHDL、Verilog-HDL、AHDL 设计层次设计层次行为描述行为描述结构描述结构描述系统级系统级算法流程图算法流程图由由Cpu或控制器、存储器等组成的逻或控制器、存储器等组成的逻辑框图辑框图寄存器传输级(寄存器传输级(RTL)数据流图、真值表、状态机、状态图数据流图、真值表、状态机、状态图(表表)寄存器、寄存器、ALU、MUX、ROM等组成等组成的逻辑图的逻辑图逻辑门级逻辑门级布尔方程、真值表、卡诺图布尔方程、真值表、卡诺图逻辑门、触发器

3、、锁存器等构成的逻逻辑门、触发器、锁存器等构成的逻辑图(网表)辑图(网表)VHDL语言语言q Very high speed integrated circuit HDLq IEEE工业标准工业标准HDL语言语言q 可支持仿真与综合可支持仿真与综合q 两个版本:两个版本:v 10761987v 10761993VHDL程序结构程序结构q 1、USE定义区定义区v Library定义所使用的元件库v Package定义所使用的元件库中的包q 2、Entity定义区:定义电路实体的定义区:定义电路实体的I/O接口规格接口规格q 3、Architecture定义区:描述电路内部具体功能定义区:描述电

4、路内部具体功能v Component定义区v 信号定义v 行为描述/数据流描述/结构描述q 4、Configuration定义区:决定使用哪一个定义区:决定使用哪一个architecture(非必须)(非必须)Use定义区定义区Library IEEE;-库定义库定义Use IEEE.std_logic_1164.all;-包引用包引用Use IEEE.std_logic_arith.all;-包引用包引用引用语句的用法:引用语句的用法:Library ,;Use lib_name.pack_name.object;PackagesPackage isConstant Decclaration

5、sType DeclarationsSignal DeclarationsSubprogram DeclarationsComponent DeclarationsOther DeclarationsEnd ;(1076-1987)End Package ;(1076-1993)Package Body isConstant DeclarationsType DeclarationsSubprogram BodyEnd Package ;(1076-1987)End Package Body (1076-1993)Package Examplepackage package_example i

6、stype life is (sleeping, working, eating, entertaiment, otheractions);subtype uint4 is integer range 0 to 15;subtype uint5 is integer range 0 to 31;function compare(a, b: integer) return boolean;end package_example;package body package_example isfunction compare(a,b: integer) return boolean isvariab

7、le temp:boolean;beginif ab thentemp:=true;elsetemp:=false;end if;return temp;end compare;end package_example;Librariesq 包括一系列的包括一系列的packagesq 隐含隐含Libraries: 不用声明,自动引用不用声明,自动引用v STD: Standard:定义bit, Boolean, integer, real和time以及支持它们的运算符。 Textio:定义文件操作。v Work: v IEEE: Std_logic_1164 Std_logic_arith St

8、d_logic_signed Std_logic_unsignedv 其它库: Altera的元件库 用户自定义库Entity(实体)(实体)q Entity定义语法Entity isgeneric declarationsport declarationsEnd ;q Entity ExampleEntity adder isgeneric(data_width:integer:=4 );port( add_a, add_b: in std_logic_vector(data_width-1 downto 0);sum: out std_logic_vector(data_width dow

9、nto 0) );End adder;Generic & Port Declarationsq Generic Declarationsv 用于将参数传入Entity。例如:数据线宽度,器件的延时参数、负载电容电阻、驱动能力、功耗等等。q Port Declarations: port_name: : v :管脚的模式 In (输入) Out (输出) Buffer (输出带内部反馈) Inout (双向)v : 数据类型 Boolean: False, True Bit: 0, 1 Std_logic: X, 0, 1, Z, -, W, L, H,支持多信号判决 Std_ulogi

10、c: 与Std_logic类型一样,不支持多信号判决 Bit_vector & std_logic_vector: Integer: NaturalPositive Real: time 自定义数据类型:如数组等Architecture(结构体)(结构体)q 描述设计的功能或者结构描述设计的功能或者结构q 必须与某个必须与某个entity相联系相联系q 一个一个entity可以对应多个可以对应多个architecture(编译时通过编译时通过configuration来指定来指定)q Architecture中的各个语句是并发执行的,对应于电路硬中的各个语句是并发执行的,对应于电路硬件

11、中的不同部件件中的不同部件q Architecture的描述风格的描述风格v 行为描述描述实体的功能,RTL级 算法描述 数据流描述v 结构描述描述实体的结构,门级v 混合描述Architecture组成组成q Architecture定义定义ARCHITECTURE arch_name OF entity_name ISsignal declarations;constant declarations;type & subtype declarations;component declarations;subprogram declarations;BEGINProcess Stat

12、ements;Concurrent Procedure Calls;Concurrent Signal Assignment;Conditional Signal Assignment;Selected Signal Assignment;Component Instantiation Statements;Generate Statements;END arch_name;结构描述例子结构描述例子半加器半加器Architecture struct_ha of half_adder iscomponent and_gate port( a1,a2: in std_logic; a3: out

13、std_logic);end component;component xor_gate port( a1,a2: in std_logic; a3: out std_logic);end component;Beging1: and_gate port map(a,b,c);g2: xor_gate port map(a,b,s);End struct_ha;行为描述例子行为描述例子半加器半加器q 算法描述算法描述Architecture behave_ha of half_adder isBegin g1:process(a,b)begin if a=1 and b=1 thenc=1; e

14、lsec=0; end if;end process; g2:process(a,b)begin if a=1 and b=0 thenc=1; elsif a=0 and b=1c=1; elsec=0; end if;end process;End struct_ha;q 数据流描述数据流描述Architecture behave_ha of half_adder isBeginc= a and b;s=a xor b;End struct_ha;Configurationq 用于将用于将entity和和architecture联系起来联系起来q 广泛应用于仿真环境广泛应用于仿真环境q 被

15、综合器有限支持或者不支持被综合器有限支持或者不支持q 语法:语法:Configuration of isfor end for;End;数据对象数据对象q Constant(常数常数)v 定义语法: Constant : := v 用符号代表常数,增加程序的可读性和可维护性v 一经定义,不得更改q Signal(信号信号)v 定义语法: Signal : := v 对应于电路中的某一节点v 通常定义于entity、architecture或者package中,全局使用v 可再赋值 : “ =”v 进程中对信号的赋值在该进程结尾才生效q Variable(变量变量)v 定义语法: Variabl

16、e : :=v 不对应于具体电路中的节点,一般用于计算用途v 只局限于进程和子程序中定义并使用v 可再赋值: “:=”v 对变量的赋值立即生效信号和变量的区别信号和变量的区别例例1q一段程序:a, b: in std_logic;x, y: out std_logic;signal temp: std_logic;process (a, b, temp)begintemp=a;x=temp;temp=b;y=temp;end process;q等价电路图:q另一段程序:a, b: in std_logic;x, y: out std_logic;process (a, b, temp) var

17、iable temp: std_logic;begintemp:=a;x=temp;temp:=b;y=temp;end process;q等价电路图:信号和变量的区别信号和变量的区别例例2q一段程序:D, clk: in std_logic;x: out std_logic;signal temp: std_logic;process (clk)begin if (clkevent and clk=1) thentemp=D;x=temp; end if;end process;q等价电路图:q另一段程序:D, clk: in std_logic;x: out std_logic;proce

18、ss (clk) variable temp: std_logic; begin if (clkevent and clk=1) thentemp:=D;x=temp; end if;end process;q等价电路图:数据类型数据类型q 基本数据类型基本数据类型v 逻辑类型: bit, boolean, std_logic, std_ulogic, std_logic_vector, bit_vectorv 整数类型: Integer(及其子类如Natural, Positive), unsigned, signedv 实数类型: Realq 高级数据类型高级数据类型v 枚举类型: 定义语

19、法:TYPE IS (, , ) 使程序易读,例如在定义状态机时v 数组类型: 定义语法:TYPE IS ARRAY (integer1 DOWNTO integer2) OF 多用于定义ROM、RAM等运算符运算符q 关系运算符:关系运算符:v = = = /=q 逻辑运算符:逻辑运算符:v and, or, not, nand, nor, xorq 算术运算符:算术运算符:v * / MOD REM * ABSq 其他运算符:其他运算符:v (正号) (负号) &(连接) q 运算符重载运算符重载v 对于不同的数据类型定义同样一个运算,其实际操作可能不同。例如+(加)运算,可以对整

20、数使用,也可以对std_loigc_vector等类型用(在std_logic_arith包中定义)。v 通常定义与package中。v IEEE的package中定义了大量的重载运算符Vector信号的分解与合并信号的分解与合并Architecture rtl of test issignal a: std_logic_vector(3 downto 0);signal b: std_logic_vector(0 to 3);signal c: std_logic_vector(0 to 1);signal d: std_logic_vector(1 downto 0);Beginc=a(2

21、 downto 1);b=A(3) & D & 1End rtl;a(3)a(2)a(1)a(0)b(0)b(1)b(2)b(3)c(0) d(1)c(1) d(0)1并发语句并发语句q VHDL程序的结构体中的各个语句是并发的,代表电路程序的结构体中的各个语句是并发的,代表电路的不同节点,它们是同时运作的的不同节点,它们是同时运作的q 并发语句的顺序不影响其执行结果并发语句的顺序不影响其执行结果q 并发语句列表:并发语句列表:v 直接信号赋值: =v 条件信号赋值:when-elsev 选择信号赋值:selectwhenv 进程:processv 断言:assert面向仿真的

22、语句,不能综合v 块语句:Blockv Component语句v For-GenerateWhen-elseq 语法:语法: = when else when else. when else ;q 特点:特点:v 各个条件可以不互斥v 主要用于译码器、多路复接器和解复接器q 例子:例子: q = a when sel=“00” elseb when sel=“01” elsec when sel=“10” elsed;abcdselqSelect-whenq 语法:语法:with select = when , when ,. when others;q 特点:特点:v 各个条件必须互斥v 主

23、要用于译码器、多路复接器和解复接器q 范例:范例: with sel selectq = a when “00”,b when “01”,c when “10”,d when others;abcdselqBlockq 用于将电路划分成几个模用于将电路划分成几个模块,增加程序的可读性块,增加程序的可读性q 语法:语法: blockBeginEnd block ;q 范例:范例:Library ieee;Use ieee.std_logic_1164.all;Entity half_addsub isport(a,b: in std_logic;sum, carry: out std_logic

24、;diff, borrow: out std_logic);End half_addsub;Architecture rtl of half_addsub isBeginHalf_adder: blocksum=a xor b;carry=a and b;End block half_adder;Half_sub: blockdiff=a xor b;borrow=(not a) and b;End block half_sub;End rtl;Componentq Component定义语句:与定义语句:与entity类似类似 Component generic ( generic_decl

25、arations );port ( port_declarations);End component;q Component例化语句:例化语句:: generic map ( generic_mapping)port map (port_mapping);q Port map语句两种格式:语句两种格式:v Port map ( =, =, );v Port map ( , , ); Component范例范例4位全加器位全加器Library ieee;Use ieee.std_logic_1164.all;Entity full_adder_4 isport( A, B: in std_log

26、ic_vector(3 downto 0); ci: in std_logic; C: out std_logic_vector(3 downto 0); co: out std_logic);End full_adder_4;Architecture rtl of full_adder_4 iscomponent full_adder_1port(a,b: in std_logic;ci: in std_logic;c: out std_logic;co: out std_logic);end component;signal t: std_logic_vector(2 downto 0);

27、BeginU0: full_adder_1port map(A(0),B(0),ci,C(0),t(0);U1: full_adder_1port map(A(1),B(1),t(0),C(1),t(1);U2: full_adder_1port map(A(2),B(2),t(1),C(2),t(2);U3: full_adder_1port map(A(3),B(3),t(2),C(3),co);End rtl;ciFull_adder_1A(0) B(0)Full_adder_1t(0)A(1) B(1)Full_adder_1t(1)A(2) B(2)Full_adder_1t(2)A

28、(3) B(3)coC(0)C(1)C(2)C(3)For-Generateq 例化多个相同的例化多个相同的Componentq 语法:语法:: For i in to generatecomponent例化语句;End generate ;q 范例范例: 4位全加器位全加器Architecture rtl of full_adder_4 is;signal t: std_logic_vector(4 downto 0);Begingen: for I in 0 to 3 generateadd1: full_adder_1 port map(A(i),B(i),t(i),C(i),t(i+1

29、);end generate gen;t(0)=ci;co=t(4);End rtl;q If-Generate语句可以条件生成。语句可以条件生成。q 生成语句可以嵌套。生成语句可以嵌套。顺序语句顺序语句q 可用于进程、函数和子程序中可用于进程、函数和子程序中q 依次执行,语句顺序影响其执行结果依次执行,语句顺序影响其执行结果q 顺序语句的执行需要被激活顺序语句的执行需要被激活q 顺序语句列表:顺序语句列表:v 变量和信号赋值::= =v If语句:if-then-elsif-elsev Case语句:case-whenv Loop语句v Wait语句Processq 特点:特点:v Proc

30、ess语句本身是一个并发式语句,但其内部包含的是顺序语句v 仅当进程的某个敏感信号发生变化时,进程内部的顺序语句块才被激活依次执行;否则进程处于被挂起的状态。v 进程内的变量在进程被挂起和再次激活时,保持原值。v 可以通过两种方式定义敏感信息:用敏感信息表或者用wait语句。但这两者不能同时出现在一个进程中(wait语句可以有多个)。q 定义语法:定义语法:Process()constant declaration;type declarations;variable declarations;Beginsequential statement #1;sequential statement

31、#2; .sequential statement #n;End process;Process范例范例Process(clk)Beginif (clkevent and clk=1) thenq=d;end if;End process;ProcessBeginwait on clk;if clkevent and clk=1 thennq=not d;end if;End process;Process敏感列表敏感列表(1)正常的代码Process (ck, d)Beginif ck=1 thenq=d;end if;End process;Max+plus II综合结果:LatchFPG

32、A Express综合结果: Latch(2)危险的代码Process (ck)Beginif ck=1 thenq=d;end if;End process;Max+plus II综合结果: D触发器FPGA Express综合结果: LatchIf语句语句q 语法:语法:If thensequential statements;Elsif thensequential statements; .Elsesequential statements;End if;q 对应于对应于when-else语句语句q 范例范例:if sel=“00” thenq=a;elsif sel=“01” the

33、nq=b;elsif sel=“10” thenq=c;elseq=d;end if;Case语句语句q 语法:语法:case is when =sequential statements; when =sequential statements; . when others=sequential statements;end case;q 对应于对应于select-when语句语句q 范例范例:case sel is when “00” =q q q q=d;end case;Loop语句语句q 无限循环:使用无限循环:使用Exit退出循环退出循环v 语法:: Loopsequential

34、statements;exit Loop_lable when ;End loop;q While循环:根据条件结束循环循环:根据条件结束循环While Loopsequential statements;End loop;q For循环:循环:FOR IN Loopsequential statements;End loop;Loop语句范例语句范例q 例1Signal a: std_logic_vector(7 downto 0)Process (a)variable temp: std_logic;Begintemp:=1;for I in 0 to 7 loop temp:=temp

35、and a(i);end loop;b=temp;End process;q 例2Signal a: std_logic_vector(7 downto 0)Process (a)variable cnt: integer;variable temp: std_logic;Begintemp:=1;cnt=0;while cnt8 loop temp:=temp and a(cnt); cnt:=cnt+1;end loop;b=temp;End process;SubprogramPackage body of example is procedure p(A: in integer, B:

36、inout integer) is begin B:=A+B; end; function inc(A: in integer) return integer is beginreturn (A+1) end;End example; q 子程序调用范例:子程序调用范例:p(a,b);x=inc(a); q 用于描述一定的算法用于描述一定的算法q 内部是串行执行内部是串行执行类似类似processq 可以在程序中任何地方被调用可以在程序中任何地方被调用q 调用方法类似于调用方法类似于Component例例化化q 综合结果是组合逻辑电路综合结果是组合逻辑电路q 包括包括function和和procedurev Function: 有返回值v Procedure: 无返回值q 子程序定义范例:子程序定义范例:Package example is procedure p(A: in integer, B:inout integ

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 浙江省杭州市杭州市第四中学2025年高二化学第二学期期末综合测试试题含解析

- 重庆实验中学2024-2025学年高二化学第二学期期末质量检测试题含解析

- 云南省红河州云南市蒙自一中2025届数学高二第二学期期末经典试题含解析

- 成都古建筑修复与保护工程合同

- 影视剧本场记职务合同规定

- 餐饮企业中央厨房租赁及生产加工合同

- 草场租赁与生态旅游开发合同

- 成都离婚协议书定制与婚姻关系终结法律支持合同

- 餐饮企业员工培训考核合同

- 杭州市上城区纪委工作人员招聘考试真题2024

- LKJ系统车载设备换装作业指导书

- 【小米公司战略成本管理分析6500字(论文)】

- 《农村电商运营》农产品电商运营方案

- 区块链在金融领域的应用课件

- VDA6.3-2016过程审核对应的资料

- 采用新技术、新工艺、新材料、新设备的安全管理措施

- 《艺术概论》章节测试及答案

- 青岛科技大学Python程序设计期末复习题

- 开曼群岛公司章程

- 爆破工程安全前提验收记录表张

- 中复神鹰碳纤维西宁有限公司年产14000吨高性能碳纤维及配套原丝建设项目环评报告

评论

0/150

提交评论