版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、电子科技大学电子科技大学1高级高级VHDL设计设计 可靠设计与高速设计可靠设计与高速设计 学时分配:学时分配:6电子科技大学电子科技大学2进度进度 1.绪论绪论 。 2.设计流程设计流程 。 3.模块化硬件与进程模型模块化硬件与进程模型 。 4.信号传输模型信号传输模型 。 5.核心语法与基础电路设计核心语法与基础电路设计 。 6.状态机设计状态机设计 。 8. 可编程逻辑器件。可编程逻辑器件。 7.可靠设计与高速设计可靠设计与高速设计 。 9.数字信号处理的数字信号处理的fpga实现实现。 10.数字系统的数字系统的RTL设计设计。声明声明 本部分内容是数字电子系统的芯片级设计中要本部分内容

2、是数字电子系统的芯片级设计中要遇到的特殊问题,虽不是考试重点,但却是实遇到的特殊问题,虽不是考试重点,但却是实际设计中的关键注意事项。际设计中的关键注意事项。 精选自一部分出版书籍、网络资料以及个人的精选自一部分出版书籍、网络资料以及个人的一些设计经验,仅仅是众多设计原则和设计技一些设计经验,仅仅是众多设计原则和设计技巧中的沧海一粟,并且错误在所难免。巧中的沧海一粟,并且错误在所难免。 艺无止境,讲授本部分的目的仅仅是带领入门,艺无止境,讲授本部分的目的仅仅是带领入门,修行仍靠自身。要熟练使用这些技巧,并且有修行仍靠自身。要熟练使用这些技巧,并且有进一步的提高,必须经过大量的项目实践去积进一步

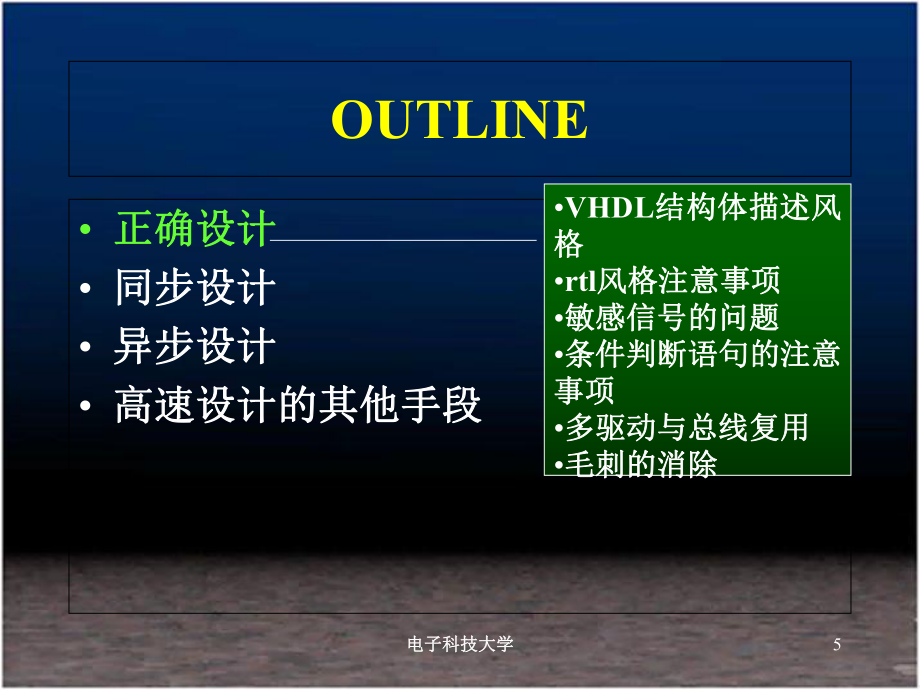

3、的提高,必须经过大量的项目实践去积累。累。电子科技大学电子科技大学4OUTLINE 正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段增加设计稳定性和工作速率的方法掺杂在这几部分内容中,不根据本部分的题目做硬性的划分。电子科技大学电子科技大学5OUTLINE 正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段VHDL结构体描述风结构体描述风格格rtl风格注意事项风格注意事项敏感信号的问题敏感信号的问题条件判断语句的注意条件判断语句的注意事项事项 多驱动与总线复用多驱动与总线复用 毛刺的消除毛刺的消除 电子科技大学电

4、子科技大学6OUTLINE 正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段VHDL结构体描述风结构体描述风格格rtl风格注意事项风格注意事项敏感信号的问题敏感信号的问题条件判断语句的注意条件判断语句的注意事项事项 多驱动与总线复用多驱动与总线复用 毛刺的消除毛刺的消除 电子科技大学电子科技大学7VHDL结构体描述风格结构体描述风格 行为描述风格行为描述风格 可进行系统仿真,少数可用于综合。可进行系统仿真,少数可用于综合。 RTL描述风格描述风格 寄存器传输级描述,也能为数据流描述寄存器传输级描述,也能为数据流描述风格。一般可被综合器综合。风格。一般可

5、被综合器综合。 结构描述风格结构描述风格 多用于顶层的模块连接。多用于顶层的模块连接。电子科技大学电子科技大学8行为描述风格行为描述风格 这种风格的描述往往以以下语句为主要特征:这种风格的描述往往以以下语句为主要特征: 使用延时语句,包括惯性延时和传输延时;使用延时语句,包括惯性延时和传输延时; 在多驱动的处理上采取判决函数;在多驱动的处理上采取判决函数; 使用使用Generic语句对时序参数建模;语句对时序参数建模; 使用其它具备行为级特性的语句如使用其它具备行为级特性的语句如wait for等语句。等语句。 这部分属于高级仿真内容,在此不作讲述。这部分属于高级仿真内容,在此不作讲述。电子科

6、技大学电子科技大学9结构体描述风格结构体描述风格 特征语句:特征语句: PORT MAP; GENERIC MAP。 不作详细讲述。不作详细讲述。电子科技大学电子科技大学10RTL描述风格描述风格 面向可综合的设计,处于抽象设计与门面向可综合的设计,处于抽象设计与门级设计之间的层次。级设计之间的层次。 其对应的硬件层次为寄存器云图其对应的硬件层次为寄存器云图电子科技大学电子科技大学11OUTLINE 正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段VHDL结构体描述风结构体描述风格格rtl风格注意事项风格注意事项敏感信号的问题敏感信号的问题条件判断语句

7、的注意条件判断语句的注意事项事项 多驱动与总线复用多驱动与总线复用毛刺的消除毛刺的消除 电子科技大学电子科技大学12RTL描述风格注意事项描述风格注意事项“X”状态的传递状态的传递时钟沿描述限制时钟沿描述限制关联性强的信号应该放在一个进程中关联性强的信号应该放在一个进程中电子科技大学电子科技大学131. “X”状态的传递状态的传递(1) 不确定态不确定态“X”在前仿真中经常会出现。当在前仿真中经常会出现。当然综合以后的时序仿真中一般是不会出现然综合以后的时序仿真中一般是不会出现的。的。 在在RTL级的描述中,要做好级的描述中,要做好“X”状态的处状态的处理,以使得前仿真和后仿真的结果一致。理,

8、以使得前仿真和后仿真的结果一致。电子科技大学电子科技大学141. “X”状态的传递状态的传递(2) 例子:例子: if( sel = 1 ) then y = 0; else y = 1; end if;从门级的观点看,该分支从门级的观点看,该分支隐含的条件为:隐含的条件为:If ( sel = 0 )。因此在后仿真时没问题,因此在后仿真时没问题,因为因为sel一般不会出现一般不会出现X。但是前仿真时,当但是前仿真时,当sel = X时,会得出时,会得出y = 1的的结果,违反了电路原理。结果,违反了电路原理。电子科技大学电子科技大学151. “X”状态的传递状态的传递(3) 例子:例子: i

9、f( sel = 1 ) then y = 0; elsif( sel = 0 ) then y = 1; else y = X; end if;加上加上X状态状态的处理。的处理。电子科技大学电子科技大学161. “X”状态的传递状态的传递(4) 实际上,第一种描述方式在设计中也是实际上,第一种描述方式在设计中也是很经常见的,但是这个时候要尽力避免很经常见的,但是这个时候要尽力避免不确定态的出现:不确定态的出现: 电路初始化要完善,特别是时序电路中要有电路初始化要完善,特别是时序电路中要有可靠的复位描述;可靠的复位描述; 尽量少用组合回环或反馈;尽量少用组合回环或反馈; 测试矢量要完善。测试矢

10、量要完善。电子科技大学电子科技大学171. “X”状态的传递状态的传递(5) 时序电路的复位例子时序电路的复位例子:时钟处理模块时钟处理模块(2分频分频) Process( clk ) Begin If( clkevent and clk = 1 ) then clk2d = not din; End if; End process;电子科技大学电子科技大学181. “X”状态的传递状态的传递(5) 时序电路的复位例子时序电路的复位例子:时钟处理模块时钟处理模块(2分频分频) Process( clk, reset_n ) Begin if( reset_n = 0 ) then clk2d

11、= 0; elsIf( clkevent and clk = 1 ) then clk2d = not din; End if; End process;注:时序电路的复位是强烈注:时序电路的复位是强烈推荐使用的,但是在某些情况推荐使用的,但是在某些情况下,复位电路会稍微降低系统下,复位电路会稍微降低系统的工作速率。是否取消复位电的工作速率。是否取消复位电路,要看具体的目标芯片和系路,要看具体的目标芯片和系统的速率需求。统的速率需求。电子科技大学电子科技大学191. “X”状态的传递状态的传递(6) 组合回环的避免组合回环的避免组合电组合电路路这种组合回环,用这种组合回环,用VHDL的逻辑运算

12、语句来描述,会无的逻辑运算语句来描述,会无法通过综合;用法通过综合;用port map语句来描述可通过综合。语句来描述可通过综合。RTL级别描述的组合回环很少使用级别描述的组合回环很少使用(并且不推荐使用并且不推荐使用),一般仅用在一些特殊场合中一般仅用在一些特殊场合中(比如多时钟切换中的毛刺比如多时钟切换中的毛刺避免等避免等),但是这在仿真时,但是这在仿真时dout往往会出现不确定态,这往往会出现不确定态,这是必须要注意的。是必须要注意的。dout电子科技大学电子科技大学202. 时钟沿描述限制时钟沿描述限制(1) 一个进程中,只能有一个时钟沿判断语句!一个进程中,只能有一个时钟沿判断语句!

13、 Process(clk1, clk2) Begin if( clk1event and clk1 = 1) then end if; if( clk2event and clk2 = 1 ) then end if; End process;电子科技大学电子科技大学212. 时钟沿描述限制时钟沿描述限制(2) 一个进程中,只能有一个时钟沿判断语句!一个进程中,只能有一个时钟沿判断语句! Process(clk) Begin if( clkevent and clk = 1) then end if; if( clkevent and clk = 1 ) then end if; End pr

14、ocess;电子科技大学电子科技大学222. 时钟沿描述限制时钟沿描述限制(3) 所以,不能在一个进程中判断两次或以所以,不能在一个进程中判断两次或以上的时钟沿,甚至是判断同一个时钟的上的时钟沿,甚至是判断同一个时钟的同一个沿也不行。同一个沿也不行。电子科技大学电子科技大学23OUTLINE 正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段VHDL结构体描述风结构体描述风格格rtl风格注意事项风格注意事项敏感信号的问题敏感信号的问题条件判断语句的注意条件判断语句的注意事项事项 多驱动与总线复用多驱动与总线复用 毛刺的消除毛刺的消除 电子科技大学电子科技

15、大学24敏感信号的问题敏感信号的问题(1)敏感信号表只对敏感信号表只对前仿真引擎前仿真引擎起作用,对起作用,对综合器综合器不起作用,而综合后生成的仿真不起作用,而综合后生成的仿真模型是保证不遗漏敏感信号的,因此设模型是保证不遗漏敏感信号的,因此设计者不小心造成的敏感信号表的遗漏往计者不小心造成的敏感信号表的遗漏往往会导致往会导致前仿真前仿真和和后仿真后仿真的不一致。的不一致。电子科技大学电子科技大学25敏感信号的问题敏感信号的问题(2)引起硬件动作的被读信号应该都放在敏引起硬件动作的被读信号应该都放在敏感信号表中,纯组合电路描述中的所有感信号表中,纯组合电路描述中的所有被读的信号都必须放在敏感

16、信号表中,被读的信号都必须放在敏感信号表中,这些信号包括:这些信号包括:组合电路描述中,所有被读取的信号;组合电路描述中,所有被读取的信号;时序电路中的时钟信号,异步控制信号。时序电路中的时钟信号,异步控制信号。敏感信号遗漏的后果可参考敏感信号遗漏的后果可参考的的p.22 p.27。电子科技大学电子科技大学26敏感信号的问题敏感信号的问题(3) 敏感信号表遗漏情况下,前仿真的波形敏感信号表遗漏情况下,前仿真的波形看起来很像锁存,因此这种错误在某些看起来很像锁存,因此这种错误在某些资料中也称为资料中也称为“仿真锁存器仿真锁存器”。电子科技大学电子科技大学27OUTLINE 正确设计正确设计 同步

17、设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段VHDL结构体描述风结构体描述风格格rtl风格注意事项风格注意事项敏感信号的问题敏感信号的问题条件判断语句的注意条件判断语句的注意事项事项 多驱动与总线复用多驱动与总线复用 毛刺的消除毛刺的消除 电子科技大学电子科技大学28条件判断语句的注意事项条件判断语句的注意事项 锁存的避免锁存的避免 无关态的使用无关态的使用 优先级问题优先级问题电子科技大学电子科技大学29锁存的避免锁存的避免 冗余锁存器的其他例子,可参考冗余锁存器的其他例子,可参考的条件判断语句部分。的条件判断语句部分。这里只做补充。这里只做补充。 例子:设计一个状态

18、机,一共有两个状态例子:设计一个状态机,一共有两个状态s0, s1。输入信号为一个比特的输入信号为一个比特的din 。当。当din = 1时,状时,状态机进行状态翻转;当态机进行状态翻转;当din = 0时,状态保持时,状态保持为当前态。为当前态。 描述方法描述方法1:可以将:可以将din当成状态机时钟当成状态机时钟clk的使的使能;本方法在此不再讲述。能;本方法在此不再讲述。 描述方法描述方法2:按照状态机描述的三进程模板进:按照状态机描述的三进程模板进行描述,以下是状态寄存器和次态译码进程。行描述,以下是状态寄存器和次态译码进程。译码输出进程省略。译码输出进程省略。电子科技大学电子科技大学

19、30 状态寄存器进程:状态寄存器进程: Process( clk, reset ) Begin if( reset = 1 )then Pst = s0; elsif( clkevent and clk = 1) then pst if( din = 1 ) then Nst = s1; else Nst . End process;在在din = 0时,初学者往时,初学者往往认为状态机不翻转,则往认为状态机不翻转,则可不必再对可不必再对Nst赋值,因赋值,因为此时为此时Nst和和Pst的值一样,的值一样,都为都为s0,再赋值一次显得再赋值一次显得多余。多余。电子科技大学电子科技大学32 事实

20、上,这个事实上,这个“多余多余”的赋值非常致命,少了这的赋值非常致命,少了这一句,电路将出现惊人的复杂化,并且工作不一句,电路将出现惊人的复杂化,并且工作不正常。因为次态译码从纯组合电路变成了锁存正常。因为次态译码从纯组合电路变成了锁存电路。电路。 思考:上一页中,初学者思路的漏洞在哪里?思考:上一页中,初学者思路的漏洞在哪里? 解答:在初始时刻,也就是在解答:在初始时刻,也就是在reset之后,如果之后,如果din = 0,则,则Nst没有获得明确的值。它只好没有获得明确的值。它只好“保持原来状态保持原来状态”。上述思路的漏洞在于没有考。上述思路的漏洞在于没有考虑到初始时刻的情况,而是假定电

21、路已经发生虑到初始时刻的情况,而是假定电路已经发生状态翻转之后再作分析。状态翻转之后再作分析。电子科技大学电子科技大学33锁存的避免锁存的避免 总结总结 组合电路描述中,条件判断语句必须指组合电路描述中,条件判断语句必须指明所有条件分支情况下,被赋值信号的明所有条件分支情况下,被赋值信号的值。值。 分支不完整,意味着电路需要在某种电分支不完整,意味着电路需要在某种电平状态下,让被赋值的信号平状态下,让被赋值的信号“保持原保持原值值”,这只能使用锁存电路实现。,这只能使用锁存电路实现。电子科技大学电子科技大学34无关态的使用无关态的使用 代码段代码段1: Case sel is when “00

22、0” = dout dout dout dout dout dout = ; End case;电子科技大学电子科技大学36 代码段代码段1的综合结果:的综合结果:doutdinadinbSel(0)Sel(1)Sel(2)电子科技大学电子科技大学37 代码段代码段2的综合结果:的综合结果:dinadinbdoutSel(1)电子科技大学电子科技大学38无关态的使用无关态的使用 总结总结 对比以上两段代码的综合结果,可以发对比以上两段代码的综合结果,可以发现,善于使用无关态现,善于使用无关态-来填补分支,可来填补分支,可以引导综合工具生成很优化的电路。以引导综合工具生成很优化的电路。 无关态无

23、关态-在本质上时起了冗余电路删简在本质上时起了冗余电路删简的作用。的作用。电子科技大学电子科技大学39优先级问题优先级问题Case语句无优先级,语句无优先级,if语句有优先级。语句有优先级。Multiple if statement和和single if statement具有两种不同的优先级顺序。具有两种不同的优先级顺序。电子科技大学电子科技大学40Single if Process( a ) Begin if ( a(0) = 1 ) then b = “001”; elsif( a(1) = 1 ) then b = “010”; elsif( a(2) = 1 ) then b = “

24、100”; else b = “000”; end if; End process;电子科技大学电子科技大学41Multiple if Process( a ) Begin b = “000”; if( a (0) = 1 ) then b = “001”; end if; if( a (1) = 1 ) then b = “010”; end if; if( a (2) = 1 ) then b = “100”; end if; End process;电子科技大学电子科技大学42OUTLINE 正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段VHD

25、L结构体描述风结构体描述风格格rtl风格注意事项风格注意事项敏感信号的问题敏感信号的问题条件判断语句的注意条件判断语句的注意事项事项 多驱动与总线复用多驱动与总线复用毛刺的消除毛刺的消除 电子科技大学电子科技大学43多驱动与总线复用多驱动与总线复用 当多个信号源同时去驱动同一个负载,当多个信号源同时去驱动同一个负载,就会形成多驱动。可暂且简单称为就会形成多驱动。可暂且简单称为输出输出碰撞碰撞。 没有处理好多驱动,不但会造成逻辑混没有处理好多驱动,不但会造成逻辑混乱,而且容易损坏器件。具体原理可参乱,而且容易损坏器件。具体原理可参考考中关于高阻中关于高阻态的内容。态的内容。电子科技大学电子科技大

26、学44多驱动与总线复用多驱动与总线复用 多驱动处理的要点:多驱动处理的要点: 行为级思维行为级思维 硬件思维;硬件思维; 总线复用;总线复用; 线与;线与; 双向端口中的高阻态;双向端口中的高阻态;电子科技大学电子科技大学45多驱动与总线复用多驱动与总线复用 多驱动处理的要点:多驱动处理的要点: 行为级思维行为级思维 硬件思维;硬件思维; 总线复用;总线复用; 线与;线与; 双向端口中的高阻态;双向端口中的高阻态; 例子:任天堂游戏机的游戏卡例子:任天堂游戏机的游戏卡(省略去省略去游戏进度存储模块游戏进度存储模块)内部的电路框图为:内部的电路框图为:Flash存储器存储器存储接口控制存储接口控

27、制Addr(23:0)csrdwrAd(15:0)A(23:16)Data(15:0)电子科技大学电子科技大学47 为了研究日本游戏技术,现在要求盗版该游戏为了研究日本游戏技术,现在要求盗版该游戏卡,其中用卡,其中用CPLD代替接口控制芯片。请写出代替接口控制芯片。请写出CPLD中,低中,低16位地址控制部分的代码。位地址控制部分的代码。 读数据读数据时低时低16位地址的控制协议:当位地址的控制协议:当cs = 0时,时,Addr(15:0) 即初始化为即初始化为Ad(15:0)的值。的值。Cs上升上升后,后,Addr(15:0)即被锁住,不再受即被锁住,不再受Ad(15:0)的的影响;在影响

28、;在cs = 1的期间,每一个的期间,每一个rd上升沿均导上升沿均导致致Addr(15:0)进行加一计数。进行加一计数。 写数据写数据时的控制也差不多,只需要将上面的时的控制也差不多,只需要将上面的rd换成换成wr即可。即可。电子科技大学电子科技大学48Addr(15:0)csrd读数据时的低读数据时的低16位地址控制时序图位地址控制时序图NN+1N+2写数据的时序图写数据的时序图基本上一样,只基本上一样,只是是rd与与wr互换互换wr电子科技大学电子科技大学49 代码实现方法代码实现方法1,包括读控制进程和写控制进,包括读控制进程和写控制进程:程: Rdproc: Process( cs,

29、rd ) Begin if( cs = 0) then Addr( 15 downto 0 ) = Ad(15 downto 0); elsif( rdevent and rd = 1 ) then Addr( 15 downto 0) = Addr( 15 downto 0) + 1; end if; End process;电子科技大学电子科技大学50 Wrproc: Process( cs, wr ) Begin if( cs = 0) then Addr( 15 downto 0 ) = Ad(15 downto 0); elsif( wrevent and wr = 1 ) then

30、 Addr( 15 downto 0) = Addr( 15 downto 0) + 1; end if; End process;电子科技大学电子科技大学51 以上代码的描述实际上以上代码的描述实际上“照搬照搬”控制协议中的描控制协议中的描述,并且符合人的述,并且符合人的“直觉思维直觉思维”。从。从“软件软件”的角的角度来看,确实没有任何算法上的错误。度来看,确实没有任何算法上的错误。 但是综合时,出现了多驱动的错误。但是综合时,出现了多驱动的错误。 原因:代码被综合成如下形式:原因:代码被综合成如下形式:Rd模块模块Wr模块模块Addr(15:0)电子科技大学电子科技大学52 这是典型的这

31、是典型的“直觉直觉”描述,没能生成正描述,没能生成正确的电路。确的电路。 修正方法如下:修正方法如下:电子科技大学电子科技大学53 rwproc: Process( cs, wr, rd ) Begin cclk = wr and rd; if( cs = 0) then Addr( 15 downto 0 ) = Ad(15 downto 0); elsif( cclkevent and cclk = 1 ) then Addr( 15 downto 0) = Addr( 15 downto 0) + 1; end if; End process;软件思维软件思维硬件思维硬件思维 的转变的转

32、变 在电路描述时,必须摒弃软件思维方式,一切在电路描述时,必须摒弃软件思维方式,一切从硬件的角度去思考代码的描述。从硬件的角度去思考代码的描述。 在具体的项目实践中,必须先画好模块的接口在具体的项目实践中,必须先画好模块的接口时序图,然后画出或者在脑子里形成模块的内时序图,然后画出或者在脑子里形成模块的内部原理框图,最后才是代码实现。部原理框图,最后才是代码实现。 企图一开始就依靠企图一开始就依靠“软件算法软件算法”思维进行代码思维进行代码实现,最后才分析时序和电路图,是非常不可实现,最后才分析时序和电路图,是非常不可取的。取的。 硬件思维的形成,需要一定的硬件设计训练才硬件思维的形成,需要一

33、定的硬件设计训练才能达到,熟练了之后才可能科学地在初始阶段能达到,熟练了之后才可能科学地在初始阶段完成模块划分和时序设计。完成模块划分和时序设计。电子科技大学电子科技大学55多驱动与总线复用多驱动与总线复用 多驱动处理的要点:多驱动处理的要点: 行为级思维行为级思维 硬件思维;硬件思维; 总线复用;总线复用; 线与;线与; 双向端口中的高阻态;双向端口中的高阻态;电子科技大学电子科技大学56总线复用总线复用 两个模块输出数据给同一个负载模块的两个模块输出数据给同一个负载模块的设计中,必须处理好总线复用。设计中,必须处理好总线复用。数据源数据源a数据源数据源b负载负载sel电子科技大学电子科技大

34、学57 加上加上sel的实质就是:的实质就是:数据源数据源a数据源数据源b负载负载seldoutadoutbdout电子科技大学电子科技大学58 或者或者数据源数据源a数据源数据源b负载负载doutadoutbdoutsel电子科技大学电子科技大学59 代码描述:代码描述: If ( sel = 1 ) then dout = douta; Else dout = doutb End if;另外:尽量不要在芯另外:尽量不要在芯片内部使用三态,某片内部使用三态,某些些FPGA不支持这种不支持这种特性,在特性,在ASIC设计中设计中也会带来一些测试上也会带来一些测试上的问题。的问题。电子科技大学电

35、子科技大学60多驱动与总线复用多驱动与总线复用 多驱动处理的要点:多驱动处理的要点: 行为级思维行为级思维 硬件思维;硬件思维; 总线复用;总线复用; 线与;线与; 双向端口中的高阻态;双向端口中的高阻态; CMOS工艺中只有漏极开路输出工艺中只有漏极开路输出(Open drain)的电路才能实现线与;的电路才能实现线与; 对应于对应于TTL工艺,则为集电极开路工艺,则为集电极开路(Open) collector)。 有部分有部分FPGA可以将引脚设置为可以将引脚设置为OD门输出,这门输出,这个时候可以实现正常的线与逻辑;但是有部分个时候可以实现正常的线与逻辑;但是有部分FPGA没有这种输出逻

36、辑,这时候可以用高阻没有这种输出逻辑,这时候可以用高阻输出或者直接切换到输入模式来代替输出或者直接切换到输入模式来代替OD模式,模式,以实现安全的线与功能。当然这个时候要在芯以实现安全的线与功能。当然这个时候要在芯片外部使用上下拉电阻来代替线与情况下的弱片外部使用上下拉电阻来代替线与情况下的弱输出。输出。 典型案例:典型案例:I2C控制模块。控制模块。I2C 模块模块SI2C 模块模块M假设某时刻,模块假设某时刻,模块M需要检需要检测到线上电平为高,才会放心测到线上电平为高,才会放心地向该信号线输出有效串行数地向该信号线输出有效串行数据,返回给模块据,返回给模块S(fpga)。fpga带带I2

37、C接口的接口的asic其他其他I2C 模块模块S电子科技大学电子科技大学63多驱动与总线复用多驱动与总线复用 多驱动处理的要点:多驱动处理的要点: 行为级思维行为级思维 硬件思维;硬件思维; 总线复用;总线复用; 线与;线与; 双向端口中的高阻态;双向端口中的高阻态;电子科技大学电子科技大学64 描述全双向端口,当描述全双向端口,当dir = 1时,数据从时,数据从da流流向向db;dir = 0时,数据从时,数据从db流向流向da。双向双向dirdadb电子科技大学电子科技大学65双向端口代码实现:双向端口代码实现:分两个方向分别描述分两个方向分别描述 - da db: If( dir =

38、1 ) then db = da; Else db = “ZZZZ”; End if; - db da: If( dir = 0 ) then da = db; Else da dqqvec110111000dclkvec001clk电子科技大学电子科技大学76时钟使能吸收时钟使能吸收计数器计数器计数器计数器clk2vecclk计数器计数器计数器计数器cevecclk注意这里注意这里ce宽度宽度为为clk的一个周期的一个周期电子科技大学电子科技大学77OUTLINE正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段同步设计的概念同步设计的概念时钟质量的保

39、证时钟质量的保证路径延迟及其优化路径延迟及其优化时钟驱动的时钟驱动的TestBench电子科技大学电子科技大学78OUTLINE正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段同步设计的概念同步设计的概念时钟质量的保证时钟质量的保证路径延迟及其优化路径延迟及其优化时钟驱动的时钟驱动的TestBench电子科技大学电子科技大学79同步设计的概念同步设计的概念整个系统有一个时钟,最多还有一些整个系统有一个时钟,最多还有一些派生派生(分频,倍频等,保证与源时钟有分频,倍频等,保证与源时钟有确定的相位关系确定的相位关系) 时钟。时钟。系统中的主要存储元件大都是

40、时钟系统中的主要存储元件大都是时钟沿敏感的元件沿敏感的元件(即寄存器即寄存器),而不是电,而不是电平敏感的元件平敏感的元件(即锁存器即锁存器)。电子科技大学电子科技大学80 数字系统设计中,应该尽量地采用纯粹数字系统设计中,应该尽量地采用纯粹的同步系统的同步系统(单时钟系统单时钟系统)设计。设计。 异步设计会给电路带来很多不安全的因异步设计会给电路带来很多不安全的因素。素。电子科技大学电子科技大学81同步系统的时序特点同步系统的时序特点 信号变化都是发生在时钟沿信号变化都是发生在时钟沿(之后的微小之后的微小时间处时间处),即系统中的动作基本上都是,即系统中的动作基本上都是“绑定绑定”在时钟沿上

41、。在时钟沿上。 信号在敏感的时钟沿之后可能会有一段信号在敏感的时钟沿之后可能会有一段不稳定时间,随后将保持一段时间的稳不稳定时间,随后将保持一段时间的稳定,等待下一个敏感的时钟沿的定,等待下一个敏感的时钟沿的采样采样。111000001电子科技大学电子科技大学82OUTLINE 正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段同步设计的概念同步设计的概念时钟质量的保证时钟质量的保证路径延迟及其优化路径延迟及其优化时钟驱动的时钟驱动的TestBench电子科技大学电子科技大学83时钟质量的保证时钟质量的保证时钟时钟Skew的最小化;的最小化;PLL的使用

42、;的使用;门控时钟与时钟使能;门控时钟与时钟使能;派生时钟与派生使能;派生时钟与派生使能;其他其他减少时钟的减少时钟的skew避免时钟毛刺避免时钟毛刺电子科技大学电子科技大学84时钟质量的保证时钟质量的保证时钟时钟Skew的最小化;的最小化;PLL的使用;的使用;门控时钟与时钟使能;门控时钟与时钟使能;派生时钟与派生使能;派生时钟与派生使能;其他其他同步系统中的时钟同步系统中的时钟skew时钟的时钟的skew(偏移,偏斜,抖动偏移,偏斜,抖动)d qd qdinq1q2clkclkddinclkclkdq1q2错误错误正确正确skew电子科技大学电子科技大学86同步系统设计中应该使时钟的同步系

43、统设计中应该使时钟的skew最最小化小化 使用快速的导线类型来对时钟布线使用快速的导线类型来对时钟布线(如如在在fpga中,采用全铜层工艺来实现全中,采用全铜层工艺来实现全局通道局通道)。使用时钟树使用时钟树(Distribution Tree)在前端设计上,应遵循一定的设计在前端设计上,应遵循一定的设计原则来避免时钟的过分偏移原则来避免时钟的过分偏移(接下去接下去一部分内容中讲述一部分内容中讲述)。电子科技大学电子科技大学87时钟质量的保证时钟质量的保证时钟时钟Skew的最小化的最小化;PLL的使用;的使用;门控时钟与时钟使能;门控时钟与时钟使能;派生时钟与派生使能;派生时钟与派生使能;其他

44、其他目前所使用的中、高目前所使用的中、高端端FPGA内部均集成内部均集成了了DPLL,甚至模拟甚至模拟锁相环。锁相环。这些锁相环提供对时这些锁相环提供对时钟的分频、倍频以及钟的分频、倍频以及移相功能,并且保证移相功能,并且保证skew最小。最小。电子科技大学电子科技大学88时钟质量的保证时钟质量的保证时钟时钟Skew的最小化的最小化;PLL的使用;的使用;门控时钟与时钟使能;门控时钟与时钟使能;派生时钟与派生使能;派生时钟与派生使能;其他其他电子科技大学电子科技大学89门控时钟门控时钟(gated clk)计数计数器器clkswdoutclkoclkclkoswdout如果将如果将sw输输入给

45、寄存器入给寄存器的时钟使能的时钟使能端端en,就可就可以基本上避以基本上避免这个误触免这个误触发发skew电子科技大学电子科技大学90Gated clk的危害的危害容易导致时序电路的误触发;容易导致时序电路的误触发;增大了增大了clk的的skew。因此在设计中,尽量避免时钟通过组合因此在设计中,尽量避免时钟通过组合电路,避免使用组合电路来产生时钟。电路,避免使用组合电路来产生时钟。Gated Clk也也不是绝对不可不是绝对不可用的,在某些用的,在某些情况下,它可情况下,它可以作为低功耗以作为低功耗设计的手段。设计的手段。电子科技大学电子科技大学91时钟质量的保证时钟质量的保证时钟时钟Skew的

46、最小化的最小化;PLL的使用;的使用;门控时钟与时钟使能;门控时钟与时钟使能;派生时钟与派生使能;派生时钟与派生使能;其他其他电子科技大学电子科技大学92 例例1:设计一个计数器系统,该系统包含:设计一个计数器系统,该系统包含两个计数器,其中一个计数器以系统时两个计数器,其中一个计数器以系统时钟钟clk频率计数;另一个计数器以频率计数;另一个计数器以clk的的1/4频率计数。频率计数。 两个计数器同时复位。假设仅要求两个计数器同时复位。假设仅要求两个计数器速度满足两个计数器速度满足4倍关系,对相位无倍关系,对相位无任何要求。任何要求。电子科技大学电子科技大学93 传统设计思路传统设计思路(暂暂

47、省略复位信号省略复位信号):Couter_aCounter_b4分频分频clkclk4ddoutadoutbclkclk4d电子科技大学电子科技大学94 优化设计思路优化设计思路Couter_aCounter_b4分频分频clken4ddoutadoutbclken4d注意注意en4d的的脉冲宽度只脉冲宽度只有一个有一个clk的的周期。周期。电子科技大学电子科技大学95选择派生使能方案的原因选择派生使能方案的原因 派生时钟方案增加了全局通道的耗费,派生时钟方案增加了全局通道的耗费,这在全局通道比较稀缺的这在全局通道比较稀缺的FPGA中是相当中是相当致命的。致命的。ASIC实现时导致了时钟树耗费

48、实现时导致了时钟树耗费增加。增加。 派生使能不但可以消除以上的缺点,而派生使能不但可以消除以上的缺点,而且其时钟且其时钟skew比派生时钟方案的比派生时钟方案的skew更更小。小。电子科技大学电子科技大学96注意派生使能的产生注意派生使能的产生 Process( clk, reset ) Begin if( reset = 1 ) then clk_vec 0 ); elsif( clkevent and clk = 1 ) then clk_vec = clk_vec + 1; end if; End process;电子科技大学电子科技大学97 Process( clk_vec ) Beg

49、in if( clk_vec = “00” ) then en4d = 1; else en4d = 0; end if; End process;注意,这里是组合注意,这里是组合电路输出电路输出en4d,难难免产生毛刺;但是免产生毛刺;但是因为因为en4d是使能信是使能信号,所以这仍然是号,所以这仍然是安全的。安全的。电子科技大学电子科技大学98(时钟质量保证时钟质量保证)小结小结(以下要点均针对前端设计以下要点均针对前端设计) 时钟的纯净时钟的纯净:时钟最好不要通过任何组:时钟最好不要通过任何组合电路,或者不要用组合电路产生时钟;合电路,或者不要用组合电路产生时钟; 时钟的单一时钟的单一:

50、数字系统设计时,应该尽:数字系统设计时,应该尽量减少时钟的数目,最好整个系统只有量减少时钟的数目,最好整个系统只有一个时钟;当需要派生时钟时,尽量用一个时钟;当需要派生时钟时,尽量用派生使能去代替。派生使能去代替。电子科技大学电子科技大学99OUTLINE正确设计正确设计 同步设计同步设计 异步设计异步设计 高速设计的其他手段高速设计的其他手段同步设计的概念同步设计的概念时钟质量的保证时钟质量的保证路径延迟及其优化路径延迟及其优化时钟驱动的时钟驱动的TestBench电子科技大学电子科技大学100时序电路的主要时序参数时序电路的主要时序参数clkDinclkDinThTsuTco电子科技大学电

51、子科技大学101路径延迟路径延迟DinclkDin组合组合电路电路TcoTcomTsu路径延迟路径延迟clk 时钟周期不时钟周期不能小于路径能小于路径延迟延迟 这里这里Tcom包含了网络包含了网络走线延迟走线延迟电子科技大学电子科技大学102路径的定义路径的定义 路径:是一系列标识一条电路的逻辑路线的元路径:是一系列标识一条电路的逻辑路线的元素;素; 路径可能包含一个信号网络路径可能包含一个信号网络(net)或一组信号网或一组信号网络络(net),以及相关的元件;,以及相关的元件; 当一个元件被包含在一条路径中时,它的输入当一个元件被包含在一条路径中时,它的输入和输出也包含在这个路径中。和输出

52、也包含在这个路径中。 路径从一个路径从一个pad或者一个同步元件或者一个同步元件(触发器触发器)的输的输出端开始,一直到遇到一个出端开始,一直到遇到一个pad或一个同步元或一个同步元件件(触发器触发器)的输入端时终止。的输入端时终止。电子科技大学电子科技大学103关键路径关键路径 一个同步系统中的关键路径,就是它所有一个同步系统中的关键路径,就是它所有的路径中,路径延迟最长的那一条。的路径中,路径延迟最长的那一条。 显然,这个同步系统的最高工作频率,等显然,这个同步系统的最高工作频率,等于关键路径延迟的倒数。于关键路径延迟的倒数。电子科技大学电子科技大学104延时优化的几个要点延时优化的几个要

53、点长路径的避免长路径的避免优先级电路的延时优化优先级电路的延时优化数据通路拷贝数据通路拷贝数据运算式变换数据运算式变换 变量运算优化变量运算优化组合路径切割组合路径切割双时钟沿问题双时钟沿问题其他其他电子科技大学电子科技大学105长路径的避免长路径的避免 实际上是一个很泛的技巧,总之,在设实际上是一个很泛的技巧,总之,在设计中,时序能走短路径就尽量走短路径;计中,时序能走短路径就尽量走短路径;组合电路能缩小就尽量缩小。以下仅举组合电路能缩小就尽量缩小。以下仅举两例来说明。两例来说明。电子科技大学电子科技大学106回忆回忆 中提出过一个问中提出过一个问题题 :状态机设计中,状态编码采用状态机设计

54、中,状态编码采用Binary编码编码和和One-hot编码对系统会造成什么样的性编码对系统会造成什么样的性能影响?这两种编码对能影响?这两种编码对FPGA/CPLD的适的适用情况如何?用情况如何?电子科技大学电子科技大学108 解答:解答:one-hot编码方式只用一个编码方式只用一个bit来表示一来表示一个状态,这大大缩小了状态译码的组合电路规个状态,这大大缩小了状态译码的组合电路规模,使得路径延时更小,因此状态机的时钟可模,使得路径延时更小,因此状态机的时钟可以运行在更高的频率上。以运行在更高的频率上。 特例:不妨想象该状态机就是一个循环计数器,特例:不妨想象该状态机就是一个循环计数器,如

55、果采用如果采用binary编码,则该计数器存在明显的编码,则该计数器存在明显的组合电路;而如果采用组合电路;而如果采用one-hot编码,该计数器编码,该计数器的综合结果就是一个移位寄存器序列,根本不的综合结果就是一个移位寄存器序列,根本不存在任何组合门!存在任何组合门!电子科技大学电子科技大学109扇入系数与组合规模扇入系数与组合规模 这个例子实际上也说明了一个问题:组这个例子实际上也说明了一个问题:组合电路的规模往往受影响于其扇入系数:合电路的规模往往受影响于其扇入系数: 扇入扇入 组合电路规模组合电路规模 从而路径延从而路径延时时 系统工作速率系统工作速率 减少组合逻辑的扇入是提高系统工

56、作速减少组合逻辑的扇入是提高系统工作速率的基本手段。率的基本手段。电子科技大学电子科技大学110 One-hot因为寄存器消耗量比较大,所以因为寄存器消耗量比较大,所以往往用在寄存器资源比较丰富的往往用在寄存器资源比较丰富的FPGA中,中,CPLD中使用得比较少。中使用得比较少。电子科技大学电子科技大学111再回忆再回忆 中的另外一个问中的另外一个问题题问题:问题:Mealy机中,机中,能否用能否用“次态次态”信号信号替代替代“输入输入”信号,信号,与与“现态现态”信号进行信号进行译码输出?译码输出?或者,保留或者,保留s5态,态,然后直接用然后直接用“次态次态”信号进行译码输出?信号进行译码

57、输出?Regs译码ClkPresent_stateQ(n)Next_stateQ(n+1) 译码DataOutZ(n)din电子科技大学电子科技大学113 对比原图:对比原图:Regs译码ClkPresent_stateQ(n)Next_stateQ(n+1) 译码DataOutZ(n)din电子科技大学电子科技大学114 经过对比发现,虽然两者在逻辑上是等经过对比发现,虽然两者在逻辑上是等效的,并且修改后的方案中似乎减少了效的,并且修改后的方案中似乎减少了输出译码电路的扇入,输出译码电路的扇入, 但是输出译码和次态译码相粘连,形成但是输出译码和次态译码相粘连,形成了一条很长的路径,导致系统工

58、作速度了一条很长的路径,导致系统工作速度下降。下降。电子科技大学电子科技大学115反馈多路选择与专用时钟使能反馈多路选择与专用时钟使能 时钟使能的两种实现方式:时钟使能的两种实现方式: 寄存器内部的专用时钟使能电路;寄存器内部的专用时钟使能电路; 反馈多路选择,如下图:反馈多路选择,如下图:10clkendindout因为增加了因为增加了额外的路径,额外的路径,因此降低了因此降低了寄存器的最寄存器的最高工作速率。高工作速率。电子科技大学电子科技大学116延时优化的几个要点延时优化的几个要点长路径的避免长路径的避免优先级电路的延时优化优先级电路的延时优化数据通路拷贝数据通路拷贝数据运算式变换数据

59、运算式变换 变量运算优化变量运算优化组合路径切割组合路径切割双时钟沿问题双时钟沿问题其他其他电子科技大学电子科技大学117优化时序的设计调整优化时序的设计调整 设计时,往往需要针对具体的情况来进设计时,往往需要针对具体的情况来进行设计的调整,以使系统的时序得到优行设计的调整,以使系统的时序得到优化。化。 时序优化的原则,最主要的还是在保证时序优化的原则,最主要的还是在保证正确逻辑的基础上,尽量缩小关键路径正确逻辑的基础上,尽量缩小关键路径的延迟。的延迟。电子科技大学电子科技大学118例:带优先级的多路选择器例:带优先级的多路选择器 假设该选择器的真值表如下:假设该选择器的真值表如下:abcds

60、elz电子科技大学电子科技大学119正常的描述方法正常的描述方法1:多:多if语句语句 Process(a, b, c, d, sel) Begin z = 0; - 要记得初始化要记得初始化!不推荐此风格。不推荐此风格。 if( sel(0) = 1 ) then z = a; end if; if( sel(1) = 1 ) then z = b; end if; if( sel(2) = 1 ) then z = c; end if; if( sel(3) = 1 ) then z = d; end if; End process;电子科技大学电子科技大学120正常的描述方法正常的描述方

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 审视过去规划未来

- 高性能合成树脂生产线项目实施方案

- 深化教育创新探索

- 生态多样性与平衡

- 难点详解人教版八年级物理上册第5章透镜及其应用-生活中的透镜定向练习试卷(含答案详解版)

- TRIZ创新方法与实例

- 考点解析-人教版八年级物理上册第4章光现象章节测评试卷(解析版含答案)

- 难点解析-人教版八年级物理上册第5章透镜及其应用-透镜单元测评试卷(解析版含答案)

- 2026年安徽广播影视职业技术学院单招职业适应性考试题库及答案1套

- 2026年云南城市建设职业学院单招职业技能考试必刷测试卷及答案1套

- 叙事护理在丁丁故事中的应用实践

- JG/T 3055-1999基桩动测仪

- 《戏曲与美术》教学课件-2024-2025学年人美版初中美术九年级上册

- 人教版数学九年级上册第一单元测试卷(附答案)

- 2025-2030年中国移植物抗宿主病(GVHD)治疗行业市场现状供需分析及投资评估规划分析研究报告

- 安全生产责任制与考核标准

- 急性ST段抬高型心肌梗死溶栓治疗专家共识解读课件

- 海鲜大排档合作协议合同

- 普通密码设备应急预案

- 受限空间作业施工方案

- DB37-T 5317-2025《旋挖成孔灌注桩施工技术规程》

评论

0/150

提交评论