版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、第第3章章 VHDL语法基础语法基础3.1 顺序语句顺序语句3.2 并行语句并行语句3.1 顺序语句顺序语句 VHDL有两种类型语句:顺序语句和并行语句并发语句)。有两种类型语句:顺序语句和并行语句并发语句)。 顺序语句的执行指仿真执行顺序是与它们的书写顺序基本顺序语句的执行指仿真执行顺序是与它们的书写顺序基本一致的。一致的。 并行语句的执行是同步进行的,或者说是并行运行的,其执行并行语句的执行是同步进行的,或者说是并行运行的,其执行方式与书写的顺序无关。方式与书写的顺序无关。 顺序语句又分两种情况:一种是真正的顺序语句。另一种具有顺序语句又分两种情况:一种是真正的顺序语句。另一种具有顺序语句

2、与并行语句的双重特性,放在进程、块、子程序之内顺序语句与并行语句的双重特性,放在进程、块、子程序之内是顺序语句,被放在进程、块、子程序之外是并行语句。是顺序语句,被放在进程、块、子程序之外是并行语句。IF语句是一种条件语句,根据语句中所设置的一种或多种语句是一种条件语句,根据语句中所设置的一种或多种条件,有选择地执行指定的顺序语句。条件,有选择地执行指定的顺序语句。条件值是布尔型条件值是布尔型TRUE或或FALSE)。)。条件条件=TRUE,执行,执行THEN后顺序语句,条件全为后顺序语句,条件全为FALSE时,时,才会执行才会执行ELSE后顺序语句或结束语句后顺序语句或结束语句END IF。

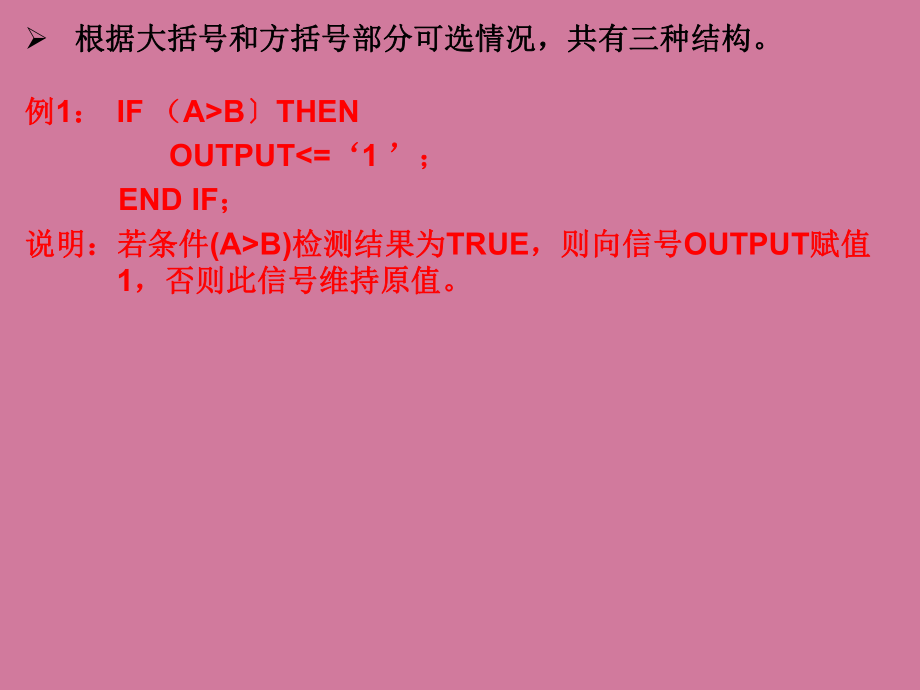

3、一、一、IF语句语句IF 条件句条件句 THEN 顺序语句;顺序语句;ELSIF 条件句条件句 THEN 顺序语句顺序语句;ELSE 顺序语句顺序语句;END IF; 语句结构:语句结构: 根据大括号和方括号部分可选情况,共有三种结构。根据大括号和方括号部分可选情况,共有三种结构。例例1: IF (ABTHEN OUTPUTB)检测结果为检测结果为TRUE,则向信号,则向信号OUTPUT赋值赋值1,否则此信号维持原值。,否则此信号维持原值。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EXAMPLE IS PORT (A,B,C: IN BOO

4、LEAN;OUTPUT:OUT BOOLEAN);END ENTITY EXAMPLE;ARCHITECTURE ART OF EXAMPLE ISBEGIN PROCESS(A,B,C) IS VARIABLE N: BOOLEAN; BEGIN IF A THEN N:=B; ELSE N:=C; END IF; OUTPUT =N; END PROCESS;END ARCHITECTURE ART;CABOUTPUT对应的硬件电路对应的硬件电路例例2:用:用IF语句描述图示硬件电路。语句描述图示硬件电路。此处的库、程序包使用此处的库、程序包使用说明是否必要说明是否必要P1P2BCBASB

5、ASAZMUX21MUX21SIGNA A,B,C,P1,P2,Z: BIT;.IF (P1=1) THENZ=A; -执行条件是执行条件是(P1=1)ELSIF (P2=0) THENZ=B; -执行条件是执行条件是(P1=0)AND (P2=0)ELSEZ=C; -执行条件是执行条件是(P1=0)AND (P2=1)END IF;例例3: 由两个由两个2选选1多路选择器构成的电路逻辑描述如图所示,多路选择器构成的电路逻辑描述如图所示,其中,当其中,当P1和和P2为高电平时下端的通道接通。为高电平时下端的通道接通。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.AL

6、L;ENTITY CODER ISPORT ( SR:IN STD_LOGIC_VECTOR(0 TO 7); SC:OUT STD_LOGIC_VECTOR(0 TO 2);END ENTITY CODER;ARCHITECTURE ART OF CODER ISBEGINPROCESS(SR) ISBEGIN IF(SR(7)=0) THEN SC=000; -(SR(7)=0) ELSIF(SR(6)=0) THEN SC =100; -(SR(7)=1) AND (SR(6)=0)ELSIF(SR (5)=0) THEN SC =010; -(SR (7)=1)AND(SR (6)=1

7、)AND(SR (5)=0)例:例:ELSIF(SR (4)=0) THEN SC =110; ELSIF(SR (3)=0) THEN SC =001;ELSIF(SR (2)=0) THEN SC =101; ELSIF(SR (1)=0) THEN SC =011; ELSESC 顺序语句;顺序语句; WHEN 选择值选择值 =顺序语句;顺序语句; WHEN OTHERS =顺序语句;顺序语句; END CASE;二、二、CASE 语句语句 符号符号=相当于相当于THEN。 执行时,首先计算表达式的值,然后将该值与执行时,首先计算表达式的值,然后将该值与WHEN中的选中的选择值比较,相同

8、执行对应的顺序语句,否则执行择值比较,相同执行对应的顺序语句,否则执行OTHERS 后后的顺序语句或结束语句的顺序语句或结束语句END CASE。 语句中的选择值必须列举穷尽,又不能重复。语句中的选择值必须列举穷尽,又不能重复。 选择值不能列举穷尽时,语句选择值不能列举穷尽时,语句WHEN OTHERS =顺序语句;顺序语句;通常不能缺省。通常不能缺省。 语句结构:语句结构:例:用例:用CASE语句描述语句描述4选选1多路选择器。多路选择器。S1S2CBADCABDS2 S1ZLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41 ISPOR

9、T(S1,S2: IN STD_LOGIC;A,B,C,D:IN STD_LOGIC; Z: OUT STD_LOGIC);END ENTITY MUX41;ARCHITECTURE ART OF MUX41 ISSIGNA S :STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINSZZZZZ=X; END CASE;END PROCESS;END ARCHITECTURE ART;S1S2CBADCABDS2 S1Z注意:本例的第五个条件名是必需的,因为对于定义注意:本例的第五个条件名是必需的,因为对于定义STD_LOGIC_VECTOR数据类型的数据类型的S,在,在VHD

10、L综合过程中,它综合过程中,它可能的选择值除了可能的选择值除了00、01、10和和11外,还可以有其他定义于外,还可以有其他定义于STD_LOGIC的选择值。的选择值。如果使用如果使用BIT_VECTOR数据类型,数据类型, WHEN OTHERS句句子就不必了。子就不必了。 X-强未知的强未知的注:书上的设计描述方法与此处不同。注:书上的设计描述方法与此处不同。三、三、LOOP语句语句 FOR-LOOP语句:语句: 标号标号:FOR 循环变量循环变量 IN 循环次数范围循环次数范围 LOOP 顺序语句顺序语句 END LOOP 标号标号; 循环变量的值在每一次的循环中都会发生变化。循环变量的

11、值在每一次的循环中都会发生变化。 循环次数范围表示循环变量在循环过程中的取值范围,显然循环次数范围表示循环变量在循环过程中的取值范围,显然FOR模式的循环次数是明确的。模式的循环次数是明确的。 LOOP语句就是循环语句,它可以使所包含的一组顺序语句语句就是循环语句,它可以使所包含的一组顺序语句被循环执行,其执行次数可由设定的循环参数决定,循环的被循环执行,其执行次数可由设定的循环参数决定,循环的方式由方式由NEXT和和EXIT语句来控制。语句来控制。例例1: 利用利用LOOP语句中的循环变量简化同类顺序语句的表达语句中的循环变量简化同类顺序语句的表达式式的使用。的使用。 SIGNA A,B,C

12、: STD_LOGIC_VECTOR(1 TO 3); FOR N IN 1 TO 3 LOOP A(N)=B(N) AND C(N); END LOOP; 说明:此段程序等效于顺序执行以下三个信号赋值操作。说明:此段程序等效于顺序执行以下三个信号赋值操作。A(1)=B(1) AND C(1);A(2)=B(2) AND C(2);A(3)=B(3) AND C(3);例例2: FOR-LOOP语句的使用语句的使用8位奇偶校验逻辑电路)。位奇偶校验逻辑电路)。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY P_CHECK IS PORT (

13、A:IN STD_LOGIC_VECTOR(7 DOWNTO 0); Y:OUT STD_LOGIC); END ENTITY P_CHECK;ARCHITECTURE ART OF P_CHECK IS SIGNAL TMP: STD_LOGIC;BEGIN PROCESS(A) IS BEGIN TMP =0; FOR N IN 0 TO 7 LOOPTMP =TMP XOR A(N); END LOOP; Y= TMP; END PROCESS;END ARCHITECTURE ART;结果:结果:Y=0 A含偶数个含偶数个1, Y=1 A含含奇数个奇数个1。WHILE-LOOP语句:语

14、句: 标号标号:WHILE 循环控制条件循环控制条件 LOOP 顺序语句顺序语句 END LOOP 标号标号; 循环控制条件为真执行顺序语句;为假结束循环。显然循环控制条件为真执行顺序语句;为假结束循环。显然WHILE模式的循环次数是未知的。模式的循环次数是未知的。 例:例: WHILE-LOOP语句的使用。语句的使用。SHIFT1: PROCESS(INPUTX) IS VARIABLE N: POSITIVE:=1; BEGIN L1: WHILE N=8 LOOP -这里的这里的“=”是小于等于的意思是小于等于的意思 OUTPUTX(N)F); S3:B(k+8):=0;K:=K+1;E

15、ND LOOP L2;END LOOP L1;EXIT- LOOP语句语句EXIT LOOP 标号标号 WHEN 条件表达式条件表达式; EXIT语句用来结束语句用来结束LOOP语句。分四种控制:语句。分四种控制: 单独单独EXIT时,无条件结束时,无条件结束LOOP语句的执行。语句的执行。 EXIT LOOP 标号标号,跳转到指定的,跳转到指定的LOOP标号处。标号处。 EXIT WHEN 条件条件,条件值,条件值=TRUE,跳出,跳出LOOP语句;条件语句;条件值值=FALSE,继续,继续LOOP循环。循环。 全不缺省时,条件值全不缺省时,条件值=TRUE,跳出,跳出LOOP语句;条件值语

16、句;条件值=FALSE,跳到指定的,跳到指定的LOOP标号处。标号处。 例:例: SIGNAL A,B:STD_LOGIC_VECTOR(1 DOWNTO 0);SIGNAL A_LESS_B:BOOLEAN;A_LESS_B=FLASE; -设初始值设初始值FOR I IN 1 DOWNTO 0 LOOPIF (A(I)=1 AND B(I)=0) THENA_LESS _B=FALSE;EXIT;ELSIF (A(I)=0 AND B(I)=1) THENA_LESS _B=TRUE; -ABEXIT; ELSE NULL;END IF;END LOOP; -当当I=1时返回时返回LOOP

17、语句继续比较语句继续比较#金金 语句格式:语句格式:标号标号 REPORT “输出字符串输出字符串” SEVERIY 出错级别出错级别 REPORT语句不增加硬件的任何功能,仿真时可用该语句提语句不增加硬件的任何功能,仿真时可用该语句提高可读性。高可读性。 REPORT语句等价于断言语句。语句等价于断言语句。 出错级别默认为出错级别默认为NOTE。四、四、REPORT语句语句例:例:WHILE COUNTER 50 THEN REPORT THE COUNTER IS OVER 50; END IF; END LOOP;NULL;空操作语句不完成任何操作,它惟一的功能就是使逻辑运行流程空操作语

18、句不完成任何操作,它惟一的功能就是使逻辑运行流程跨入下一步语句的执行。跨入下一步语句的执行。NULL常用于常用于CASE语句中,为满足所有可能的条件,利用语句中,为满足所有可能的条件,利用NULL来表示所余的不用条件下的操作行为。来表示所余的不用条件下的操作行为。五、空操作语句五、空操作语句(NULL)例:在例:在CASE语句中,语句中,NULL用于排除一些不用的条件。用于排除一些不用的条件。CASE OPCODE IS WHEN “001”= TMP := REGA AND REGB; WHEN “101”= TMP := REGA OR REGB; WHEN “110”= TMP := N

19、OT REGA; WHEN OTHERS = NULL; END CASE;#成成3.2 并行语句并行语句相对于传统的软件描述语言,并行语句结构是相对于传统的软件描述语言,并行语句结构是VHDL特色。特色。在在VHDL中,并行语句具有多种语句格式,各种并行语句在中,并行语句具有多种语句格式,各种并行语句在结构体中的执行是同步进行的并行运行),其执行方式与结构体中的执行是同步进行的并行运行),其执行方式与书写的顺序无关。书写的顺序无关。在执行中,并行语句之间可以有信息往来,也可以是互为独在执行中,并行语句之间可以有信息往来,也可以是互为独立、互不相关、异步运行立、互不相关、异步运行(如多时钟情况

20、如多时钟情况)。并行语句在结构体中的使用格式如下:并行语句在结构体中的使用格式如下:ARCHITECTURE 结构体名结构体名 OF 实体名实体名 IS 说明语句;说明语句;BEGIN 并行语句;并行语句;END ARCHITECTURE 结构体名;结构体名;结构体中的并行语句模块结构体中的并行语句模块 生生成成语语句句条条件件信信号号赋赋值值语语句句元元件件例例化化语语句句并并行行信信号号赋赋值值语语句句块块语语句句进进程程语语句句并并行行过过程程调调用用语语句句信号信号信号信号信号信号信号信号信号信号信号信号ARCHITECTUREEND ARCHITECTURE结构体中各种并行语句运行的

21、示意图如下。每一语句模块都结构体中各种并行语句运行的示意图如下。每一语句模块都可以独立异步运行,模块之间是并行运行,并通过信号来交可以独立异步运行,模块之间是并行运行,并通过信号来交换信息。在实际编程中这些语句不必同时存在。换信息。在实际编程中这些语句不必同时存在。 其赋值目标必须是信号。其赋值目标必须是信号。 信号赋值语句其所有可读入信号是隐性的,任何信号的变化信号赋值语句其所有可读入信号是隐性的,任何信号的变化都会启动语句的赋值操作。都会启动语句的赋值操作。 并行信号赋值语句有三种形式:简单信号赋值语句、条件信并行信号赋值语句有三种形式:简单信号赋值语句、条件信号赋值语句和选择信号赋值语句

22、。号赋值语句和选择信号赋值语句。二、信号代入语句并行信号赋值语句)二、信号代入语句并行信号赋值语句)注意:信号赋值用注意:信号赋值用“”符号,两边数据类型的一致。符号,两边数据类型的一致。 一、变量赋值语句一、变量赋值语句目标变量名目标变量名:=表达式;表达式; 简单信号赋值语句简单信号赋值语句 信号赋值目标表达式;信号赋值目标表达式;注意:变量赋值用注意:变量赋值用“:=”符号,两边数据类型必须一致。符号,两边数据类型必须一致。 例:例:ARCHITECTURE ART OF XHFZ IS SIGNA S1: STD_LOGIC; BEGIN OUTPUT 1= A AND B; OUTP

23、UT 2= C+D;B1:BLOCK SIGNA E, F, G, H: STD_LOGIC; BEGIN G=E OR F; H=E XOR F;END BLOCK B1;S1=G;END ARCHITECTURE ART并行语句并行语句并行语句并行语句并行语句并行语句条件信号赋值语句条件信号赋值语句 信号赋值目标信号赋值目标 表达式表达式1 WHEN 条件条件1 ELSE 表达式表达式2 WHEN 条件条件2 ELSE 表达式表达式3 WHEN 条件条件3 ELSE 表达式表达式n WHEN 条件条件n ELSE 表达式表达式n+1;根据赋值条件的书写顺序逐项测定,一旦发现赋值条件根据赋值

24、条件的书写顺序逐项测定,一旦发现赋值条件=TRUE,便将对应的表达式的值赋给目标,否则将最后一个,便将对应的表达式的值赋给目标,否则将最后一个表达式的值赋给目标。表达式的值赋给目标。注:书上有错。注:书上有错。例:例:Z= A WHEN P1=1 ELSE B WHEN P2=0 ELSE C;选择信号赋值语句选择信号赋值语句 WITH 选择表达式选择表达式 SELECT 信号赋值目标信号赋值目标 表达式表达式1 WHEN 选择值选择值1 表达式表达式2 WHEN 选择值选择值2 表达式表达式n WHEN 选择值选择值n; 表达式表达式n+1 WHEN OTHERS; 每当选择表达式的值发生变

25、化时,将其值与各子句中的选择每当选择表达式的值发生变化时,将其值与各子句中的选择值作比较,比较结果相等的子句获得赋值资格。值作比较,比较结果相等的子句获得赋值资格。 不允许有条件重叠现象。也不允许存在条件涵盖不全的情况,不允许有条件重叠现象。也不允许存在条件涵盖不全的情况,否则最后一句不能缺省。否则最后一句不能缺省。 不能在进程中使用。不能在进程中使用。 例:下图是一个简化的指令译码器。对应于由例:下图是一个简化的指令译码器。对应于由A、B、C三个位三个位构成的不同指令码,由构成的不同指令码,由DATA1和和DATA2输入的两个值将进行不输入的两个值将进行不同的逻辑操作,并将结果从同的逻辑操作

26、,并将结果从DATAOUT输出。输出。DECODERBCADATA1DATAOUTDATA2LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECODER ISPORTA,B,C:IN STD_LOGIC; DATA1,DATA2: IN STD_LOGIC; DATAOUT:OUT STD_LOGIC););END DECODER;ARCHITECTURE ART OF DECODER IS SIGNAL INSTRUCTION:STD_LOGIC_VECTOR2 DOWNTO 0);); BEGIN INSTRUCTION=C&B&a

27、mp;A; WITH INSTRUCTION SELECT DATAOUT OUTPUT OUTPUT OUTPUT OUTPUT=S1;END CASE;END IFEND PROCESS P1;END ARCHITECTURE ART;例例2: 含敏感信号表的进程语句。含敏感信号表的进程语句。SIGNA CNT4:INTEGER RANGE 0 TO 15; -注意注意CNT4的数据类型的数据类型.PROCESS(CLK,CLEAR,STOP) IS -该进程定义了该进程定义了3个敏感信号个敏感信号 CLK、CLEAR、STOPBEGIN -当其中任何一个改变时,都将启动进程的运行当其中任

28、何一个改变时,都将启动进程的运行IF CLEAR=0 THENCNT4=0;ELSIF CLKEVENT AND CLK=1THEN -如果遇到时钟上升沿,那么如果遇到时钟上升沿,那么IF STOP=0THEN -如果如果STOP为低电平,则进行加法计数,否则停止计数为低电平,则进行加法计数,否则停止计数CNT4=CNT4+1; END IF;END IF;END PROCESS; WAIT 语句语句WAIT -无限等待无限等待WAIT ON 信号表信号表-敏感信号量变化敏感信号量变化WAIT UNTIL 条件表达式条件表达式 -表达式成立时进程启动表达式成立时进程启动WAIT FOR 时间表

29、达式时间表达式 -时间到,进程启动时间到,进程启动 当遇到当遇到WAIT时,运行程序将被挂起暂停运行),只有满足时,运行程序将被挂起暂停运行),只有满足WAIT中设置的结束挂起条件后,才会继续运行程序。中设置的结束挂起条件后,才会继续运行程序。 单独单独WAIT表示永远挂起。表示永远挂起。 WAIT ON 信号表,称为敏感信号等待语句。表中的敏感信号信号表,称为敏感信号等待语句。表中的敏感信号发生变化时,结束挂起,再次启动进程。发生变化时,结束挂起,再次启动进程。 WAIT UNTIL 条件表达式条件表达式 属条件等待。当表达式中信号发生属条件等待。当表达式中信号发生改变,并且为改变,并且为T

30、RUE时,结束挂起,执行时,结束挂起,执行WAIT之后的语句。之后的语句。此格式可被综合器综合,其它格式只能在仿真器中使用。此格式可被综合器综合,其它格式只能在仿真器中使用。 进程中使用了进程中使用了WAIT语句后,经综合就会产生时序逻辑电路。语句后,经综合就会产生时序逻辑电路。 VHDL规定,已列出敏感量的进程中不能使用规定,已列出敏感量的进程中不能使用WAIT语句。语句。例例1: WAIT ON S1,S2; -S1,S2是敏感信号,其中任一信号发生变化时如由是敏感信号,其中任一信号发生变化时如由0变或由变或由1变变0),就结束挂起,执行),就结束挂起,执行WAIT之后的语句。之后的语句。

31、 例例2:以下两种表达方式是等效的。:以下两种表达方式是等效的。 WAITUNTIL结构结构 WAIT UNTIL ENABLE=1; WAITON结构结构 LOOP WAIT ON ENABLE EXIT WHEN ENABLE=1; END LOOP例例3: WAIT UNTIL语句的三种表达方式:语句的三种表达方式:WAIT UNTI 信号信号=VALUE;WAIT UNTI 信号信号EVENT AND 信号信号=VALUE;WAIT UNTI NOT 信号信号STABLE AND 信号信号=VALUE;注:其中注:其中EVENT和和STABLE是预定义的信号检测属性函数。是预定义的信号

32、检测属性函数。EVENT:测试信号的有事件发生。:测试信号的有事件发生。例如,语句例如,语句CLOCK EVENT就是对就是对CLOCK信号,在信号,在当前的一个极小的时间段内发生事件的情况进行检测。所当前的一个极小的时间段内发生事件的情况进行检测。所谓发生事件,就是电平发生变化,从一种电平方式转变到谓发生事件,就是电平发生变化,从一种电平方式转变到另一种电平方式。如果在此时间段内,另一种电平方式。如果在此时间段内,CLOCK由由0变成变成1或或由由1变成变成0都认为发生了事件,于是返回一个都认为发生了事件,于是返回一个BOOLEAN值值TRUE,否则为,否则为FALSE。STABLE:与:与

33、EVENT恰好相反,测试信号的无事件发生。恰好相反,测试信号的无事件发生。 如果设如果设CLOCK为时钟信号输入端,以下四条为时钟信号输入端,以下四条WAIT语句所语句所设的进程启动条件都是时钟上跳沿,它们对应的硬件结构是一样设的进程启动条件都是时钟上跳沿,它们对应的硬件结构是一样的。的。WAIT UNTI CLOCK =1;WAIT UNTI CLOCKEVENT AND CLOCK=1 ;WAIT UNTI NOT CLOCKSTABLE AND CLOCK=1;WAIT UNTI RISING_EDGE(CLOCK);注:注:RISING_EDGE是一个预定义的信号上升延测试函数。是一个

34、预定义的信号上升延测试函数。例例4:设计一个硬件电路,求:设计一个硬件电路,求4个数的平均值。个数的平均值。 PROCESS BEGIN WAIT UNTIL CLK=1; AVE=A; WAIT UNTIL CLK=1; AVE=AVE+A; WAIT UNTIL CLK=1; AVE=AVE+A; WAIT UNTIL CLK=1; AVE=(AVE+A)/4; END PROCESS;例例5:在一个进程中,有一无限循环的:在一个进程中,有一无限循环的LOOP语句,其中语句,其中WAIT语语句描述了一个具有同步复位功能时钟到才复位的电路。句描述了一个具有同步复位功能时钟到才复位的电路。 P

35、ROCESS BEGIN SRT_LOOP:LOOP WAIT UNTIL CLOCK=1 AND CLOCKEVENT; NEXT RST_LOOP WHENRST=1);); X=A; WAIT UNTIL CLOCK=1AND CLOCKEVENT; NEXT RST_LOOP WHENRST=1);); YL-TIME,GB2=S-TIME);-局部端口局部端口参量设定参量设定PORT (PB1:IN BIT;PB2:INOUT BIT);-块结构中局部端块结构中局部端口定义口定义POTR MAP(PB1=B1,PB2=A1); -块结构端口连接说明块结构端口连接说明CONSTANT

36、DELAY:TIME:=1 ms; -局部常数定义局部常数定义SIGNA S1:BIT; -局部信号定义局部信号定义BEGINS1=PB1 AFTER DELAY; PB2=S1 AFTER GB1; END BLOCK BLK1;END ARCHITECTURE ART;B1:BLOCK-定义块定义块B1 SIGNAL S:BIT; -在在B1块中定义块中定义S BEGIN S=A AND B; -向向B1中的中的S赋值赋值 B2:BLOCK -定义块定义块B2,套于,套于B1块中块中 SIGNAL S:BIT; -定义定义B2块中的信号块中的信号S BEGIN S=C AND D; -向向

37、B2中的中的S赋值赋值 B3:BLOCK BEGIN Z=S; -此此S来自来自B2块块 END BLOCK B3; END BLOCK B2; YVALUE:=“0101”; WNEN“0101”=VALUE:=“0000”; WNEN OTHERS=VALUE:=“1111”;END CASEEND PROCEDURE PRG1;例例2: PROCEDURE COMPA,R:IN REAL;M:IN INTEGER; V1,V2:OUT REALISVARIABLE CNT:INTEGER;BEGIN V1:=1.6*A; V2:=1.0; Q1:FOR CNT IN 1 TO M LOO

38、P V2:=V2*V1; EXIT Q1 WHEN V2R; END LOOP Q1; ASSERT( V2 实参表达式实参表达式 ,形参名形参名 实参表达式实参表达式); 过程名是被调用过程的名字。过程名是被调用过程的名字。 实参表达式又称实参,为具体数值或标识符。实参表达式又称实参,为具体数值或标识符。 形参名是过程中定义的参数名,在调用时形参被实参替代。形参名是过程中定义的参数名,在调用时形参被实参替代。 形参被实参替代的方法有两种:位置关联法和名字关联法。形参被实参替代的方法有两种:位置关联法和名字关联法。 例:例:PACKAGE DATA_TYPES IS TYPE DATA_ELE

39、MENT IS INTEGER RANGE 0 TO 3; TYPE DATA_ARRAY IS ARRAY(1 TO 3) OF DATA _ELEMENT ;END DATA_TYPES ;USE WORK. DATA_TYPES .ALL;ENTITY SORT IS PORT(IN_ARRAY: IN DATA_ARRAY; OUT_ARRAY: OUT DATA_ARRAY);END SORT;ARCHITECTURE ART OF SORT IS BEGIN PROCESSIN_ARRAY) PROCEDURE SWAPDATA:INOUT DATA_ARRAY; LOW,HIGH

40、:IN INTEGERIS-SWAP的形参名为的形参名为DATA、LOW、HIGH VARIABLE TEMP: DATA _ELEMENT ; BEGIN IFDATALOW)DATAHIGH)THEN TEMP:= DATALOW);); DATALOW) := DATAHIGH);); DATAHIGH) := TEMP ; END IF; END SWAP; VARIABLE MY_ARRAY: DATA_ARRAY; BEGIN MY_ARRAY:= IN_ARRAY; SWAP( MY_ARRAY,1,2););- MY_ARRAY 、1、2是对应于是对应于DATA、LOW、HIG

41、H的实参的实参 SWAP( MY_ARRAY,2,3);); -位置关联法调用,第位置关联法调用,第2、第、第3元素交换元素交换 SWAP( MY_ARRAY,1,2););-位置关联法调用,第位置关联法调用,第1、第、第2元素再次交换元素再次交换 OUT_ARRAY= MY_ARRAY; END PROCESS;END ART; 函数语句函数语句FUNCTION)FUNCTION 函数名参数表函数名参数表RETURN 数据类型数据类型 IS 说明部分说明部分 BEGIN 顺序语句顺序语句 END FUNCTION 函数名;函数名;六、函数和函数调用六、函数和函数调用 参数表用于定义输入值,只

42、能是信号或常量参数表用于定义输入值,只能是信号或常量 ,并且无须指定,并且无须指定工作模式工作模式 。RETURN 数据类型数据类型指的是返回值数据类型。指的是返回值数据类型。 说明部分是对函数体内的用到的数据类型、常量、变量等作说明部分是对函数体内的用到的数据类型、常量、变量等作局部说明。局部说明。 顺序语句用以完成规定算法或各种转换等。函数被调用时,顺序语句用以完成规定算法或各种转换等。函数被调用时,执行的就是这部分语句。执行的就是这部分语句。 函数调用函数调用 函数调用与过程调用相似,差异是函数的参量只能是输入值,函数调用与过程调用相似,差异是函数的参量只能是输入值,并且返回一个指定数据

43、类型的值。并且返回一个指定数据类型的值。例:例:ENTITY FUNC IS PORT(A;IN BIT_VECTOR0 TO 2);); M:OUT BIT_VECTOR( 0 TO 2););END FUNC1;ARCHITECTURE ART OF FUNC IS FUNCTION SAMX,Y,Z:BITRETURN BIT IS BEGIN RETURNX AND YOR Z; END FUNCTION SAM; BEGIN PROCESSA) BEGIN M0)=SAMA0),),A1),),A2);); M1)=SAMA2),),A0),),A1);); M2)=SAMA1),)

44、,A2),),A0);); END PROCESS;END ART;RETURN 表达式表达式;返回语句只能用于子程序过程、函数中,结束子程序的执行。返回语句只能用于子程序过程、函数中,结束子程序的执行。 RETURN格式,只能用于过程,只是结束过程,不返回任何值。格式,只能用于过程,只是结束过程,不返回任何值。 RETURN 表达式表达式格式,只能用于函数,必须返回一个值。表格式,只能用于函数,必须返回一个值。表达式提供函数返回值。达式提供函数返回值。 函数至少含一个返回语句,也可以拥有多个返回语句,但调用时函数至少含一个返回语句,也可以拥有多个返回语句,但调用时只能有一个返回语句将值带出。

45、只能有一个返回语句将值带出。 七、返回语句七、返回语句RETURN) 例例1: 在一过程定义中在一过程定义中,完成一个完成一个RS触发器的功能。触发器的功能。PROCEDURE RSSIGNAL S,R:IN STD_LOGOC; SIGNAL Q,NQ:INOUT STD_LOGOC) ISBEGIN IFS=1 AND R=1)THEN REPORT “FORBIDDEN STSTE:S AND R ARE EQUAL TO 1 ”; RETURN ELSE Q=S AND NQ AFTER 5 ns; NQ=S AND Q AFTER 5 ns; END IF;END PROCEDURE

46、 RS;例例2: FUNCTION OPT(A,B,OPT:STD_LOGIC) RETURN STD_LOGIC ISBEGIN IFOPR=1)THEN RETURUA AND B);); ELSE RETURNA OR B);); END IF;END FUNCTION OPR;说明:此函数功能是:当说明:此函数功能是:当OPR为高电平时,返回为高电平时,返回A AND B的值;当的值;当OPR为低电平时,返回为低电平时,返回A OR B的值。的值。REN_VALUABOPR函数函数OPT的电路结构图的电路结构图ASSERT 条件条件REPORT报告信息报告信息SEVERITY出错级别出

47、错级别;断言语句主要用于程序仿真,调试中的人断言语句主要用于程序仿真,调试中的人-机会话。综合器通常机会话。综合器通常忽略此语句。忽略此语句。ASSERT语句判断指定的条件是否为语句判断指定的条件是否为TRUE,如果为,如果为FALSE则报则报告错误。告错误。报告信息:必须是用报告信息:必须是用“ ”括起来的字符串类型的文字。括起来的字符串类型的文字。出错级别:必须是出错级别:必须是SEVERITY_LEVEL类型。类型。REPORT子句默认时,报告信息为子句默认时,报告信息为Assertion Violation,即违,即违背断言条件。背断言条件。若若SEVERITY子句默认,默认出错级别为

48、子句默认,默认出错级别为error。任何并行断言语句任何并行断言语句(ASSERT)都对应等价一个被动进程语句。都对应等价一个被动进程语句。并行断言语句并行断言语句ASSERT的条件以静态表达式定义时,这个断言的条件以静态表达式定义时,这个断言语句等价于一个无敏感信号的以语句等价于一个无敏感信号的以WAIT语句结尾的进程。语句结尾的进程。八、并行断言语句八、并行断言语句(ASSERT)例:例:ASSERT NOT (S=1 AND R=1)REPORT BOTH VALUES OF SIGNALS S AND R ARE EQUA TO1SEVERITY ERROR;注意:如果出现注意:如果出

49、现SEVERITY子句,则该子句一定要指定一个类型子句,则该子句一定要指定一个类型为为SEVERITY_LEVEL的值。的值。SEVERITY_LEVEL共有如共有如下四种可能的值:下四种可能的值:NOTE注意):可以用在仿真时传递信息。注意):可以用在仿真时传递信息。WARNING警告):用在非平常的情形,此时仿真过程仍可继警告):用在非平常的情形,此时仿真过程仍可继续,但结果可能是不可预知的。续,但结果可能是不可预知的。ERROR错误):用在仿真过程继续执行下去已经不可能的情错误):用在仿真过程继续执行下去已经不可能的情况。况。FAILURE失败):用在发生了致命错误,仿真过程必须立即失败

50、):用在发生了致命错误,仿真过程必须立即停止的情况。停止的情况。COMPONENT 元件名元件名 GENERIC类属表)类属表) PORT元件端口名表)元件端口名表)END COMPONENT ;九、元件调用语句(九、元件调用语句( COMPONENT ) 该语句可用于该语句可用于ARCHITECTURE,PACKAGE,Block的说明的说明部分。部分。 元件调用语句又称元件定义语句,其作用是对设计实体进行元件调用语句又称元件定义语句,其作用是对设计实体进行封装,只留出界面的接口芯片的引脚)。封装,只留出界面的接口芯片的引脚)。 元件名就是封装元件名就是封装芯片的名字。芯片的名字。 在该语句

51、中间可以有在该语句中间可以有GENERIC语句和语句和PORT语句。语句。 GENERIC语句用于该元件参数的代入或赋值。语句用于该元件参数的代入或赋值。 PORT语句用于该元件的输入、输出端口信号的规定语句用于该元件的输入、输出端口信号的规定 。元件。元件端口名表列出对外通信的各端口名芯片的各引脚名)。端口名表列出对外通信的各端口名芯片的各引脚名)。 标号名:元件名标号名:元件名 PORT MAP( 元件端口名元件端口名连接实体端口名,连接实体端口名,);); 十、端口映射语句十、端口映射语句PORT MAP) 端口映射语句的作用是为元件配上指定的插座。标号名就是插端口映射语句的作用是为元件

52、配上指定的插座。标号名就是插座名,元件名是由座名,元件名是由COMPONENT语句定义的。语句定义的。 PORT MAP是端口映射的意思。其中的元件端口名是指芯片是端口映射的意思。其中的元件端口名是指芯片的引脚;连接实体端口名是指插座的引脚。符号的引脚;连接实体端口名是指插座的引脚。符号“”表示表示两脚相连。两脚相连。 端口映射的表达方式有两种:一种是名字关联方式,另一种是端口映射的表达方式有两种:一种是名字关联方式,另一种是位置关联方式。位置关联方式。 在元件的调用过程中,在元件的调用过程中, COMPONENT语句和语句和PORT MAP语语句都必须存在。句都必须存在。 参数传递语句参数传

53、递语句GENERIC ) GENERIC ( 常数名:数据类型常数名:数据类型:设定值:设定值 ; 常数名:数据类型常数名:数据类型:设定值:设定值 ; ););十一、参数传递和参数映射语句十一、参数传递和参数映射语句注:注: GENERIC语句在第一章的幻灯中已作过详细的介绍,在语句在第一章的幻灯中已作过详细的介绍,在此不再重复。此不再重复。 参数映射语句参数映射语句GENERIC MAP ) 标号名:元件名标号名:元件名 GENERIC MAP实参实参1,实参,实参2,实参实参N);); GENERIC MAP的作用就是参数映射,其中的标号名和元件名的作用就是参数映射,其中的标号名和元件名

54、与与PORT MAP中的含义一样,中的含义一样, 实参实参1,实参,实参2,实参实参N指的是实际参数值,映射的表达方式指的是实际参数值,映射的表达方式采用位置关联方式。采用位置关联方式。例例1:设计图示的:设计图示的VHDL描述程序。描述程序。A1U1U2Z1U3B1C1D1ABABABCCCS1S2ND2ND2ND2方法:方法: 首先完成一个首先完成一个2输入与非门的设计,然后用输入与非门的设计,然后用COMPONENT语语句和句和PORT MAP语句对该元件进行调用。语句对该元件进行调用。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ND2

55、 IS PORTA,B:IN STD_LOGIC; C:OUT STD_LOGIC););END ND2;ARCHITECTURE ARTND2 OF ND2 IS BEGIN CC1,C = S2,B = D1););-名字关联方式名字关联方式 U3:ND2 PORT MAPS1,S2,C = Z1);); -混合关联方式混合关联方式END ARCHITECTURE ARTORD41 ;A1U1U2Z1U3B1C1D1ABABABCCCS1S2ND2ND2ND2ENTITY and2 IS GENERIC (rise,fall: TIME);-参数类型说明参数类型说明 PORT (a,b:

56、IN BIT; C: OUT BIT);END and2;ARCHITECTURE generic_example OF and2 IS SIGNAL d: BIT; BEGIN d = a and b; C AI),),Y=BI););END GENERATE GEN;例例1:用生存语句产生:用生存语句产生8个相同的电路块。个相同的电路块。A0COMPINPUTOUTPUTB0A1COMPINPUTOUTPUTB1A7COMPINPUTOUTPUTB7RANGE是预定义的属性函数,是预定义的属性函数,在此对信号在此对信号A的元素排序按指的元素排序按指定要求约束(定要求约束( 0 TO 7 )

57、。)。另外有另外有REVERSE_RANGE属属性函数,元素排序按逆序排列。性函数,元素排序按逆序排列。例例2:8位三态锁存器位三态锁存器74LS373的设计。通过元件的调用和的设计。通过元件的调用和FORGENERATE语句进行描述。语句进行描述。 74LS373引脚功能引脚功能: D1D8为数据输入端;为数据输入端; Q1Q8为数据输出端;为数据输出端; OEN为输出使能端,若为输出使能端,若OEN=1,则,则Q8Q1的输出为高阻态,的输出为高阻态,若若OEN=0,则,则Q8Q1的输出为保存在锁存器中的信号值;的输出为保存在锁存器中的信号值; G为数据锁存控制端,若为数据锁存控制端,若G=

58、1,D8D1输入端的信号进入输入端的信号进入74LS373中的中的8位锁存器中,若位锁存器中,若G =0,74LS373中的中的8位锁存位锁存器将保持原先锁入的信号值不变。器将保持原先锁入的信号值不变。74LS373D8D7D6D5D4D3D2D1OENGQ8Q7Q6Q5Q4Q3Q2Q1 74LS373内部逻辑结构内部逻辑结构:OENLATCHLATCHLATCHLATCHLATCHLATCHLATCHLATCHQ QQ QQ QQ QQ QQ QQ QQ QENAD DENAD DDENADDENADDENADDENADDENADDENADGD8D7D6D5D4D3D2D1OT11OT11O

59、T11OT11OT11OT11OT11Q8Q7Q6Q5Q4Q3Q2Q1OT11LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LATCH IS PORT(D:IN STD_LOGIC; ENA:IN STD_LOGIC; Q:OUT STD_LOGIC);END ENTITY LATCH;ARCHITECTURE ONE OF LATCH ISSIGNA S0: STD_LOGIC; BEGIN PROCESS(D,ENA) IS BEGIN IF ENA=1 THEN S0=D; END IF; Q=S0; END PROCESS;END ARCHITECTURE ONE; 一位锁存器一位锁存器LATCH的逻辑描述的逻辑描述OENLATCHLATCHLATCHLATCHLATCHLATCHLATCHLATCHQ QQ QQ QQ QQ

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 煤炭居间人合同范本

- 2025年湖北恩施学院辅导员招聘考试真题汇编附答案

- 产品开发及产品管理面试题含答案

- 2026年一级注册建筑师之建筑结构考试题库300道【b卷】

- 2025辽宁沈阳盛京资产管理集团有限公司所属子公司沈阳华海锟泰投资有限公司所属子公司招聘5人考试笔试备考题库及答案解析

- 美术教师聘用合同范本

- 承包配送食品合同范本

- 炉工雇佣合同范本

- 2026年机械员之机械员基础知识考试题库300道(含答案)

- 企业内部人力资源培训师选拔题库参考

- 南阳市劳务合同范本

- 产业园招商培训

- 2026年齐齐哈尔高等师范专科学校单招综合素质考试题库必考题

- 2018版公路工程质量检验评定标准分项工程质量检验评定表路基土石方工程

- 导尿管相关尿路感染(CAUTI)防控最佳护理实践专家共识解读

- 2025年广东深圳高中中考自主招生数学试卷试题(含答案详解)

- SMETA员工公平职业发展管理程序-SEDEX验厂专用文件(可编辑)

- 2024年湖南高速铁路职业技术学院公开招聘辅导员笔试题含答案

- 水泵购买合同(标准版)

- ICU获得性衰弱课件

- 数字智慧方案5912丨智慧军营建设方案

评论

0/150

提交评论