汽车自动清洗机PLC控制系统设计【全套5张CAD图纸和毕业论文】【汽车专业】

收藏

资源目录

压缩包内文档预览:

编号:334211

类型:共享资源

大小:2.41MB

格式:RAR

上传时间:2014-09-26

上传人:好资料QQ****51605

认证信息

个人认证

孙**(实名认证)

江苏

IP属地:江苏

45

积分

- 关 键 词:

-

汽车

自动

清洗

plc

控制系统

设计

全套

cad

图纸

毕业论文

专业

- 资源描述:

-

【温馨提示】 购买原稿文件请充值后自助下载。

[全部文件] 那张截图中的文件为本资料所有内容,下载后即可获得。

预览截图请勿抄袭,原稿文件完整清晰,无水印,可编辑。

有疑问可以咨询QQ:414951605或1304139763

目 录

摘要 I

Abstract II

第1章 绪 论 1

1.1 课题研究的目的意义 1

1.2 课题的国内外研究现状 2

第2章驱动桥的总体方案确定 3

2.1 驱动桥的种类结构和设计要求 3

2.1.1 汽车车桥的种类 3

2.1.2 驱动桥的种类 3

2.1.3 驱动桥设计要求 6

2.2 设计车型主要参数 4

2.3 主减速器结构方案的确定 4

2.3.1 主减速比的计算 4

2.3.2 主减速器的齿轮类型 4

2.3.3 主减速器的减速形式 5

2.3.4 主减速器主从动锥齿轮的支承形式及安装方法 8

2.4 差速器结构方案的确定 8

2.5 半轴的形式确定 8

2.6 桥壳形式的确定 9

2.7 本章小结 9

第3章 主减速器设计 10

3.1 概述 10

3.2 主减速器齿轮参数的选择与强度计算 10

3.2.1 主减速器计算载荷的确定 10

3.2.2 主减速器齿轮参数的选择 11

3.2.3 主减速器齿轮强度计算 22

3.2.4 主减速器轴承计算 26

3.4 主减速器的润滑 33

3.4 主减速器的润滑 33

3.5 本章小结 33

第4章 差速器设计 34

4.1 概述 34

4.2 对称式圆锥行星齿轮差速器原理 34

4.3 对称式圆锥行星齿轮差速器的结构 34

4.4 对称圆锥行星锥齿轮差速器的设计 35

4.4.1 差速器齿轮的基本参数选择 35

4.4.2 差速器齿轮的几何尺寸计算 36

4.4.3 差速器齿轮的强度计算 38

4.4.4 差速器齿轮的材料 39

4.5 本章小结 39

第5章 半轴设计 40

5.1 概述 40

5.2 半轴的设计与计算 40

5.2.1 全浮式半轴的计算载荷的确定 40

5.2.2 半轴杆部直径的初选 41

5.2.3 全浮式半轴强度计算 42

5.2.4 全浮式半轴花键强度计算 42

5.2.5 半轴材料与热处理 44

5.3 本章小结 44

第6章 驱动桥桥壳的设计 45

6.1 概述 45

6.2 桥壳的受力分析及强度计算 45

6.2.1 桥壳的静弯曲应力计算 45

6.2.2 在不平路面冲击载荷作用下桥壳的强度 47

6.2.3 汽车以最大牵引力行驶时的桥壳的强度计算 47

6.2.4 汽车紧急制动时的桥壳强度计算 49

6.3 本章小结 51

结论 52

参考文献 53

致谢 54

附录 55

附录A 外文文献中文翻译 55

附录B 外文文献原文 57

摘 要

轻型汽车在商用汽车生产中占有很大的比重,而且驱动桥在整车中十分重要。它的性能的好坏直接影响整车性能,而对于载货汽车显得尤为重要。设计出结构简单、工作可靠、造价低廉的驱动桥,能大大降低整车生产的总成本。

本文首先确定主要部件的结构型式和主要设计参数,在分析驱动桥各部分结构形式、发展过程及其以往形式的优缺点的基础上,确定了总体设计方案,采用传统设计方法对驱动桥各部件主减速器、差速器、半轴、桥壳进行设计计算并完成校核。最后运用AUTOCAD完成装配图和主要零件图的绘制。

关键词:驱动桥;主减速器;差速器;半轴;桥壳

Abstract

Pickup trucks take a large proportion of commercial vehicles production, and the drive axle is one of the most important structure. Drive axle is the one of automobile four important assemblies, its performance directly influence on the entire automobile, especially for the truck .Because using the big power engine with the big driving torque satisfied the need of high speed, heavy-loaded, exploiting the high driven efficiency single reduction final drive axle is becoming the trucks’ developing tendency.

In this paper, first of all determine the structure of major components and the main design parameters, determined on the basis of the design program, using the traditional design method of various parts of the drive axle Main reducer, differential, axle, axle housing was designed to calculate and complete the check. Finally complete the final assembly drawing by using AUTOCAD and mapping the main components.

Keywords:Drive Hxle; Reduction Final Drive; Differential; Axle;

Drive Axle Housing

- 内容简介:

-

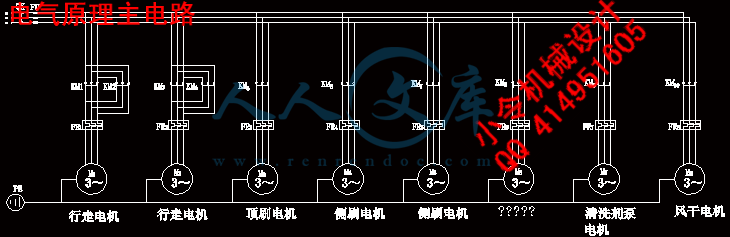

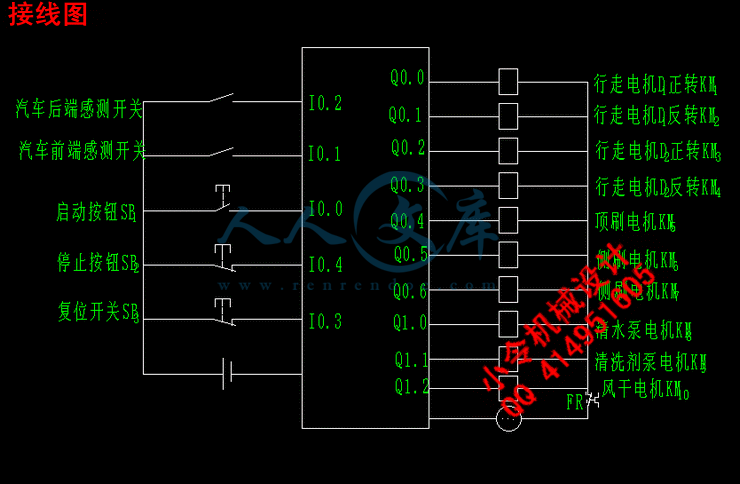

编号无锡太湖学院毕业设计(论文)相关资料题目: 汽车自动清洗机PLC控制系统设计 信机 系 机械工程及自动化专业学 号: 0923106学生姓名: 钱 辉 指导教师: 黄 敏 (职称:副教授 ) (职称: )2013年5月25日目 录一、毕业设计(论文)开题报告二、毕业设计(论文)外文资料翻译及原文三、学生“毕业论文(论文)计划、进度、检查及落实表”四、实习鉴定表无锡太湖学院毕业设计(论文)开题报告题目: 汽车自动清洗机PLC控制 系统设计 信机 系 机械工程及自动化 专业学 号: 0923106 学生姓名: 钱 辉 指导教师: 黄 敏 (职称:副教授 ) (职称: )2012年11月25日 课题来源自拟科学依据(包括课题的科学意义;国内外研究概况、水平和发展趋势;应用前景等)(1) 课题科学意义随着我国汽车保有量的持续增加,汽车清洗作为汽车保养的一个前提工序,就显得越来越重要。开发汽车自动清洗机对于节约水资源和环境保护,提高劳动生产率具有重要意思。本课题属工程设计类课题,要求完成汽车自动清洗机的PLC控制系统设计。通过本设计,可以帮助学生加深对本专业的相关知识理解和提高综合运用专业知识能力(2) 汽车自动清洗机研究概况汽车清洗是近儿年才在我国逐渐发展起来的新兴行业,具备资金和技术门槛低的特点。由于从国家到地方,相关的行业标准不是十分完备,对场地、环保、设备、技术、经营管理等方面都缺乏明确的规定和要求,导致本应被淘汰地洗车方式仍然在洗车市场上大行其道,而无水洗车、全白动电脑机械化洗车等先进的洗车方式却在市场份额中占有很小的比例。在欧、美等发达国家,经过多年的发展,科学洗车的理念己深入人心,洗车市场的洗车方式有全自动电脑洗车机洗车、燕汽洗车和无水洗车,其中尤以全自动电脑洗车为主。在我国建设、美化城市,创建现代化城市的发展土题中,在全社会节约水资源、保护环境、可持续发展的潮流中,追求时尚、效率和环保已成为汽车美容服务行业的重要内容和发展方向。目前,城市落后的人工洗车方式己不能适应现代化城市的市容卫生和行业发展的需求,也不符合企业的规模经营、专业化、规范化的要求,更谈不上行业的可持续发展。要想中国的洗车行业健康有序地发展,当务之急,必须推广科学的、环保的、符合中国国情的科学洗车方式,要用新的理念、新的思路和新的方法来管理洗车行业,提升行业的形象和竞争力。全自动电脑洗车机,顺应时代的需要应运而生。它的出现是向传统洗车方式的挑战,必将引起洗车行业市场一场激烈的竟争和带来根本性的变革。中国的洗车行业要发展,必须与国际洗车业接轨,缩小与国际先进洗车行业的差距。因此,推广和应用全自动洗车机势在必行。研究内容(1) 了解汽车自动清洗机的工作原理,国内外的研究发展现状;(2) 完成汽车自动清洗机控制系统设计; 全白动洗车机的总体方案设计 全自动洗车机电气控制系统设计 全自动洗车机PLC控制系统软件设计(3) 完成有关工艺流程设计、控制系统主电路、控制电路和电气元件的选型设计。(4) 熟练掌握有关计算机绘图软件,并绘制有关电路图纸,编制PLC控制程序;完成设计说明书的撰写,并翻译外文资料1篇。拟采取的研究方法、技术路线、实验方案及可行性分析通过对汽车清洗机功能要求和运行过程的分析,确定汽车清洗机的总体设计方案,对水循环处理系统进行设计。并主要进行汽车清洗机驱动和控制系统的设计。针对汽车清洗机的特点,采用电力和气压驱动两种驱动方式,为后续精密控制顶刷、侧刷和吹干系统的运行满足仿形要求创造了条件。在控制部分,应用传感器和可编程序控制器技术,对汽车清洗机PLC控制系统进行了硬件设计和控制软件编程。研究计划及预期成果研究计划:2012年11月12日-2012年12月2日:按照任务书要求查阅论文相关参考资料,填写毕业设计开题报告书2012年12月3日-2013年1月20日:进入工厂实习,了解企业生产流程。2013年2月11日-2月16日:查找一篇关于PLC的的英文资料,并完成翻译。2013年2月18日-3月9日:确定汽车自动清洗机的总体方案以及主电路图。2013年3月11日-3月16日:电路中电动机选型。2013年3月18日-2013年3月30日:确定I/O地址分配及接线图。2013年4月1日-2013年4月13日:完成PLC的选型以及编写梯形图。2013年4月15日-2013年5月10日:撰写论文和相关资料。2013年5月13日-2013年5月25日:完成论文,准备答辩。预期成果:按照计划完成本课题的设计,可以基本实现汽车自动清洗机的工作要求。所设计的控制程序,能够基本实现。特色或创新之处(1)主题明确,有针对性,安全,效率高,通用性强。(2)使用简易,功能完善,成本较低。已具备的条件和尚需解决的问题条件:PLC控制的基础知识,与课题相关的资料、期刊、文摘等问题:PLC的编程软件及一些汽车清洗机方面的知识指导教师意见 指导教师签名:年 月 日教研室(学科组、研究所)意见 教研室主任签名: 年 月 日系意见 主管领导签名: 年 月 日英文原文Journal of Software Engineering and Applications, 2011, 4, 172-180doi:10.4236/jsea.2011.43019 Published Online March 2011 (http:/www.SciRP.org/journal/jsea)Development of Equivalent Virtual Instruments to PLC Functions and NetworksMohammad A. K. Alia, Tariq M. Younes, Mohammad Abu ZalataMechatroncis Engineering Department, Faculty of Engineering Technology, Al-Balqa Applied University, Amman, Jordan.Email: makalalia2000, tariqmog, abuzalataReceived February 20th, 2011; revised March 5th, 2011; accepted March 10th, 2011. ABSTRACTThis research is a continuation to our work which was published in 1. Eight different timing VIs are designed and tested. These include ON-Delay, OFF-Delay, Single Shot, Retriggerable Monostable, and Accumulative software-based timers. Using hardware programmable counter/timer chip (DAQ-STC-24bit) and PCI MIO-16E-1 DAQ board, another two precise timers are designed. At the end of the paper, for illustration purposes, an electro-pneumatic drive system was developed and controlled utilizing designed on-delay timers VI functions. Results of experiment show complete coincidence between the PLC-based control and Virtual PLC-based program results.Keywords: PLC, Virtual PLC, LabVIEW, Programmable Timers1. IntroductionIn our work “Design of a virtual PLC using LabVIEW” we have shown how it is possible to create LabVIEW VIs which represent PLC functions and networks. We compared between PC-based and PLC-based control systems, and came to the fact that both systems are continuously developing in the same direction in order to obtain better programmability, connectivity and communication interfacing. At the time being the PC-based DCSs are suited for industrial applications. They are robust and they easily work in an open architecture mode, while PLCs are equipped with specific MMI software and pseudo-standard commutation software also. We have shown that in order to improve the programmability of PACs, we practically brought the PLC to the computer utilizing by that numerous advantages of computers such as multitasking, unlimited memory, high speed and the possibility of creating unlimited number of programmable objects such as counters, timers, shift registers and others. Because of the limited size of previous work, we were not able to cover other important VIs which may be used also as the analog of PLC functions. In this paper we shall develop different types of programmable timers using LabVIEW software 2 and NI DAQ board hardware also. The LabVIEW basic functions that provide timing on millisecond level are the “wait” and “wait for Next ms Multiple” VIs. Both are based on the same under lying mechanism. Most applications work comfortably with available LabVIEW measurements that resolve milliseconds, and many more operate with second resolution3-4. A few applications demand sub-millisecond resolution and response time, which is problematic due primarily to operating system and not a LabVIEW limitation5. If the application requires higher accuracy or resolution than the built-in timing functions can supply, then one will have to use some additional hardware, such as NI-DAQ boards or an external clock 6. NI-boards have two 24bit counter chips and several on-board clocks that can be counted to produce accurate timing (intervals). With the DAQ counter-timer VIs, one can configure the on-board versatile hardware for a variety of tasks including the accurate generation of timed pulses, counting events, and the measurement of periods and frequencies. The counter output generates a pulse when a preprogrammed terminal count (TC) is reached. The pulse may be used for sequencing purposes. Similar hardware-based timing may be performed using windows API function “Query performance counter”. This function looks at a high resolution system hardware counter that runs at approximately 1.2 MHz or 0.8 microsecond count. The actual resolution, once we account for the delay in calling the function, will be considerably less, but still far better than one millisecond. Concerning Real-Time operating systems (RTOS), they are designed to run a single program with very precise timing. They can allow to run loops with nearly the same thing each iteration (typically within microseconds). Timing for hard RTOSs can be performed using the DAQ cards internal clock, giving better accuracy than software timing functions 7. At the time being, some hardware platforms feature an on-board FPGA, that may be programmed using LabVIEW FPGA module. NI ComactRIO and single-board RIO are examples. The default clock rate of LabVIEW FPGA is 40 MHz. General FPGA timing VIs 2 may generate one clock period. One-shot pulse or measure the period, pulse width, accumulate period over a specified number of pulses and count pulses over a specified period of time. Nevertheless FPGA VIs do not include ready On-delay timers, OFF-delay timers and momostable retriggerable timers which find extensive applications in PLC sequential control programs. Building on the above, the target of this work is to illustrate the design of different types of timing VIs using LabVIEW software in order to be used as programming elements in virtual PLC programs. 2. ON-Delay Timer1) ON-Delay Timer-1Figure 1 shows the front panel and the block diagram components of a software-based ON-Delay Timer. The loop iteration is indicated in seconds. Because the loop iteration starts from zero, the increment function is added in order to start it at one. Since the wait icon has 100 ms delay between every two iterations a factor of 10 is multiplied by timer preassigned value, in order to measure the time delay in seconds. After the application of enable signal it takes some delay time interval for the equal function to have a true state at the output. If the input signal is disabled, the timer output instantly changes to low state.2) ON-Delay Timer-2The components of the VI are shown in the block diagram, Figure 2. Initially the input signal is not enabled and the false case is activated. The output of select icon will be zero, which is lower than the timer preset value, and as a result of that the output of the timer is OFF. When the input signal is enabled the true case is executed and the select icon will output the value that comes form the output of the case structure. The initial value of the iteration local variable is zero, then it will be incremented after a delay caused by the wait icon, and then compared by timer preset value. When the output of the comparison function is true, the output of the timer becomes high. When the enable input signal becomes low, the output of the timer becomes low simultaneously. In this VI, the checking of the case structure is continuous at a scan rate equal to one millisecond, which is accepted for many applications. (a)(b)(c)Figure 1. On-delay timer-1, (a) The Block Diagram; (b) The Front Panel; (c) Subicon3. OFF-Delay Time1) OFF-Delay Timer-1The front panel and block diagram are shown in Figure3. The while loop and other VI components are located inside the false case of the case structure. The true case has a local variable of the timer output, which is wired to the selector terminal. The enable input signal is connected to the selector terminal of the false case.2) OFF-Delay Timer-2The block diagram is given in Figure 4. When the input is enabled the true case is activated and the select icon will be selected to zero. In this case the output of the comparison function is false and the timer output is true. When the input signal is disabled the false case executes, and the select icon is selected to the value that comes from the output of the case structure. When the off-delay time interval elapses the output of the comparison function is true and the timer output is false.(a)(b)Figure 4. OFF delay timer 4, (a) True case; (b) False case4. Single-Shot TimerThe block diagram and front panel are shown in Figure 5. The Boolean indicator prevents the timer output to turn ON again after the elapse of the preset value of one-shot timer. During the false case the output is OFF, and during the comparison time the timer output enabled high. At the end of comparison the timer output is low again.5. Retriggerable Monostable Timer VIFigure 6 shows the block diagram and the front panel of this timer. When the enable input switches ON, the timer output immediately turns ON and the timer starts timing. As soon as the preset time value has elapsed, the timer output switches OFF, even if the enable input is still ON. Every OFF to ON transition of the enable input resets the timer, i.e. the elapsed time is set to pre-set value and timer output is switched ON. Figure 7 shows a three mode delay timer. ON delay, OFF delay and Retriggerable Monostable timers are built in one block diagram, where the programmer can select the required timer mode. 6. Accumulative TimerVIThe timer block diagram and front panel are shown in Figure 8. The output of the add function and the timer preset value are connected to the equal comparison function. The output equal comparison function is connected to one terminal of the OR gate. The other input of the OR gate function is connected to the inverted input signal. The output of OR function is connected to conditional terminal of the while loop.(a)(b)(c)Figure 3. OFF-delay timer, (a) The block diagram; (b) The front panel; (c) Subicon.The conditional terminal is connected to one terminal of the AND gate. The other input of the AND gate is connected to local variable of the input signal. The output of the AND gate is the timer output. The while loop and above mentioned components are inside the true case of the case structure. When the input signal is not enabled the false case is activated, then the local variable of accumulative indicator has a zero value and that value will be stored in the current time indicator. The true case will be activated when the input signal is enabled. If the input signal is disabled before the equal comparison function is true, the false case is activated and the local variable of the loop iteration has that value at which the loop was stopped and this value will be stored in the current time indicator. If the input signal is activated again, the true case is activated and the previous operation is repeated again, where the loop iteration is added to the previous value, which is stored in the current timer indictor, then it is compared with the timer preset value. The process of enabling and displaying the input signal continues until the output of the equal comparison function becomes true and as a result the timer output turns ON. Figure 9 shows a designed VI in order to measure time interval in the range of nanoseconds. A hardware programmable counter/timer chip (DAQSTC-24 bit )and a hardware time base signal source located on PCI-MIO-16E-1 DAQ-Board are utilized. The program is built using the advance subVIs because they are more flexible than the easy VIs or intermediate VIs. A closely related issue is the use of two hardware counters for measurement of sampling time interval. In such a case the signal of interest is fed to a counter source terminal and to the gate terminal of another counter. The source terminal of the second counter is fed by a periodic clock signal with a much higher frequency than the expected sampling frequency. Normally, the internal time base of the counter provides more than adequate source to count (i.e. 20 MHZ and above). To receive an accurate indication of the time, both counters must start at the same instant. By diving the count of the second counter by the frequency we find the time. As an example, we shall consider an electro-pneumatic drive system. The drive circuit is given in Figure 10. PLC input/output assignments are given in Table 1. Input/output channels assignment for LabVIEW DAQboard are given in Table 2. System operation sequence is as follows:In order to initialize operation an external pushbutton is used. As a result of that solenoid valve (SV) is energized and cylinder out strokes. At the end of stroke the cylinder actuates limit switch (LS), which, enables an ON-Delay timer (T1). After the elapse of the timer preset time value the (SV) is deenergized and returns to its initial position. At this instance ON-Delay timer (T2) is enabled, up counter CTU is incremented, the timer T1 is disabled, and the solenoid valve is actuated again and the sequence repeats. The sequence is continued until the counter instantaneous count is equal to counter preset value and the sequence stops. For Siemens PLC (S7-214), the ladder diagram is shown in Figure 11, and the equivalentLabVIEW ladder diagram is shown in Figure 12. Experimental results show completely coincidence between both diagrams 7. ConclusionsUsing LabVIEW environment, seven different timing virtual instruments have been designed and tested. Applying the same approach it is possible to design a complete set of PLC functions in order to realize able PC-based virtual PLC. In this case the virtual PLC will gain the advantages of PC-Based control.REFERENCES1 M. K. Abuzalata, M. A. Alia, et al., “Designing Virtual PLC Using LabVIEW”, Applied Sciences Engineering and Technology, Maxwell Science Publication, UK, Vol.2, No. 3, 2010, p. 288.2 “Function and VI Reference Manual,” National Instruments,1998 Edition, Austin, USA.3 K. L. A. Shley, “Analog Electronics with LabVIEW,” Prentice Hall PTR, 2003.4 T. Mohioddin and M. Nawroki, “LabVIEW Advance Programming Techniques,” Second Edition, CRC Press, Boca Raton, 2006.5 J. Essick, “Hands-on Introduction to LabVIEW for Scientists and Engineers,” Oxford University Press, USA,2008.6 J. Y. Beyon, “Hands-on Exercise Manual for LabVIEW Programming, Data Acquisition and Analysis,” Prentice Hall PTR, USA, 2003.7 B. E. Paton, “Sensors, Transducers and LabVIEW,” Prentice Hall International (UK) Limited, London, 1993.中文译文软件工程与应用,学报2011,4,172 - 180 开发与PLC功能和网络等效的虚拟仪器Mohammad A. K. Alia, Tariq M. Younes, Mohammad Abu ZalataReceived February 20th, 2011; revised March 5th, 2011; accepted March 10th, 2011.摘要本研究是对我们工作的一个延续,发表在1。设计和测试了八个不同的时间VIs。这包括延迟打开、延迟断开、单发射击、可在触发的单稳态、累计计时器软件。使用硬件可编程计数器/定时器芯片设计(DAQ-STC-24bit)和PCI MIO-16E-1 DAQ板两个精确的计时器。在本文的结尾,开发一个电动气动驱动系统和利用对延迟计时器控制设计VI功能,来解释。实验结果显示基于plc程序控制和基于plc虚拟两者之间的结果是一致的。关键词:可编程控制器,PLC虚拟,虚拟仪器,可编程定时器1、 介绍我们的工作“使用虚拟仪器设计虚拟PLC”,我们已经表明我们可以创建代表的PLC功能和网络的虚拟仪器。我们比较基于PC和基于PLC的控制系统,来得到两个系统不断在同一方向发展以取得更好的可编程性、连通性和连通接口。同时基于PC的DCSs是适合工业应用的。他们是健大的和他们轻松地工作在一个开放的架构模式,虽然PLC是配备特定的MMI软件和伪标准变换软件。我们表明,为了提高的可编程性PACs,我们几乎把计算机的众多优点的PLC作为多任务,无限的记忆,高速和可能创造出无限数量的可编程对象如计数器、计时器、移位寄存器和其他。因为之前的工作规模有限,我们不能覆盖其他重要的工作,使用和模拟PLC功能。本文我们开发不同类型的使用虚拟仪器软件2和NI DAQ板硬件的可编程定时器。虚拟仪器的基本功能,提供时间在毫秒级的“等待”和“等待多个“VIs。两者都是基于相同的底层机制。大多数应用程序工作的舒适,可用虚拟仪器测量,解决毫秒,更多的操作与第二分辨率3 - 4。一些应用程序的需求和响应时间毫秒级的决议,这是有问题的,主要是由于操作系统,而不是一个虚拟仪器限制5。一些应用程序的需求和响应时间毫秒级的决议,这是有问题的,主要是由于操作系统,而不是一个虚拟仪器限制5。如果应用程序需要更高的精度和分辨率比内置定时功能可以供应,那么你将不得不使用一些额外的硬件,比如我董事会或外部时钟6。镍板有两个24位计数器芯片和一些船上的时钟,可以算出精确定时(时间间隔)。与DAQ计数器定时器VIs、一个可以配置车载多功能硬件来完成各种任务,包括精确定时,计数脉冲生成事件,和测量时间和频率。产生一个脉冲计数器输出当预排程序的终端数(TC)是达到了。脉冲可以用于排序的目的。类似的基于硬件的时机可能是使用windows API函数进行“查询性能计数器”。这个函数看起来在一个高分辨率的系统硬件计数器运行大约在1.2 MHz或0.8微秒数。实际的分辨率,一旦我们帐户延期,调用该函数,将大大减少,但仍远比一个毫秒。关于实时操作系统(RTOS),它们被设计为运行一个程序非常精确定时。他们可以允许运行循环几乎同样的事情每个迭代(通常在微秒)。硬RTOSs时机可以执行使用DAQ卡的内部时钟,给予更好的精度比软件定时功能7。当时,一些硬件平台功能的FPGA,这可能是使用FPGA模块编程虚拟仪器。NI ComactRIO和单板是例子。默认的时钟频率的FPGA是40 MHz虚拟仪器。通用FPGA定时VIs2可能会生成一个时钟周期。一次性脉冲或测量周期、脉冲宽度、积累期超过指定数量的脉冲和计数脉冲在指定的一段时间。然而FPGA VIs不包括准备在延迟定时器,定时器和momostable延迟断开可再触发的计时器,找到广泛应用于PLC顺序控制程序。建立在上面的,这个工作的目标是说明设计不同类型的定时VIs使用虚拟仪器软件为了被用作编程元素在虚拟PLC程序。2、 接通延时时间1)、接通延时-1图1显示了前面板和程序框图的组件软件在延迟计时器。循环迭代显示秒。由于循环迭代开始从零,增加功能被添加以启动它在一个。因为等待图标有100毫秒的延迟每两个迭代之间的10倍乘以定时器预先指定的值,为了测量时间延迟在秒。应用程序的启动信号后,它需要一些延迟时间间隔相等的功能有一个真正的状态输出。如果输入信号是禁用的,定时器输出立即改变低状态。2)接通延时-2VI的组件显示在框图2。最初输入信号不启用和虚假的情况下被激活。选择图标的输出是0,即低于预设值,定时器的结果是输出的计时器是关闭的。当输入信号是使真正的案件执行,选择图标将输出值,来自输出案例的结构。迭代初始值的局部变量是零,那么它将增加所造成的延迟后等待图标,然后由定时器预设值相比。当比较函数的输出是正确的,输出的定时器就高。当允许输入信号就低,输出的计时器同时就低。在这个VI,检查案例的结构是连续在一个扫描速率等于一毫秒,接受许多应用程序。(a)(b)(3)在延迟定时器,(a)框图;(b)面板(c)功能3、关闭延时1)关闭延时-1前面板和方块图是图3所示。当循环和其他VI组件的位置在错误的情况下的情况下结构。真实的案例有一个局部变量定时器的输出,这是连接到选择器终端。允许输入的信号连接到选择器终端的虚假情况。2)关闭延时-2给出了框图如图4。当输入是启用的情况下被激活的真实和选择图标将被选定为零。在这种情况下,输出的比较函数是假和定时器输出是正确的。当输入信号是禁用的虚假案件执行,选择图标被选中的值来自输出案例的结构。当关闭延迟时间间隔过后比较函数的输出是真的和定时器输出是假的。(a)(b)(a)真(b)假4、单发定时器和前面板的框图如图5所示。布尔指示器防止定时器输出后再打开的推移预设值一次性计时器。在错误的情况下,输出是关闭的,在比较时间定时器输出使高。最后比较计时器再次低输出。5、可再触发的单稳态定时器VI图6显示了框图和前面板的计时器。当允许输入开关,定时器输出立即打开,计时器开始计时。一旦预定时间价值已经运行,定时器输出开关关闭,即使允许输入

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

人人文库网所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

川公网安备: 51019002004831号

川公网安备: 51019002004831号